# Embedded controller for a fully suspended active magnetic bearing system

D.E. Vogel B.Eng.

Dissertation submitted to The School of Electrical, Electronic and Computer Engineering in partial fulfilment of the requirements for the degree Master of Engineering in Computer and Electronic Engineering at North-West University

Supervisor:Prof. G van SchoorAssistant Supervisor:Mr. E.O. Ranft

June 2006

Potchefstroom Campus

# **Declaration**

I hereby declare that all the material incorporated in this dissertation is my own original unaided work except where specific reference is made by name or in the form of a numbered reference. The work herein has not been submitted for a degree at another university.

Signed: \_\_\_\_\_\_ Deon Edward Vogel

# Summary

The industrial application of active magnetic bearings is expanding. This expansion is a driving force in the integration of AMBs. The Magnetic Bearing Modelling and Control (MBMC) research group in the School of Electrical, Electronic and Computer Engineering, North-West University is accordingly compelled to expand their research to the application of embedded control systems. The aim of this study is to develop an embedded controller for an active magnetic bearing in order to establish a DSP platform for future research in embedded control systems.

The embedded controller developed during this study is required to be capable of actively controlling a spindle with a rotaional speed of 60 000 rpm. It is further required that the embedded controller is capable of stand-alone operation, scalable in terms of the number of axes controlled and flexible in terms of the control algorithm implementation.

A TMS320F2812 DSP is selected for its processing speed, on-chip peripherals and available development tools such as the eZdsp<sup>®</sup> TMS320F2812 DSP Starter Kit, VisSim<sup>®</sup> Embedded Controls Developer and Code Composer Studio<sup>®</sup>. The interface of the embedded controller is designed for an existing double radial AMB model, which allows for the performance of the embedded controller to be compared to the existing PC-based controller.

The AMB system exhibits a slightly higher second order equivalent stiffness and damping when using the embedded controller as opposed to the existing PC-based controller. The AMB system is also slightly less sensitive when using the embedded controller.

This embedded controller establishes a DSP platform which can be used for further research into embedded control systems and advanced control algorithms. The knowledege gained and controller developed for this study serves as essential stepping stones towards the ultimate goal of AMB integration through the progression from a DSP to an FPGA and eventually an ASIC.

# Opsomming

Die industriële aanwending van aktiewe magnetiese laers (AMLs) is besig om uit te brei. Hierdie uitbreiding dien as 'n dryfveer vir die integrasie van AMLs. Die Magnetiese Laer Modellering en Beheer navorsingsgroep in die Skool vir Elektriese, Elektroniese en Rekenaar Ingenieurswese aan die Noordwes Universiteit is dienooreenkomstig gemotiveer om hulle navorsing uit te brei na die toepassing van ingebedde beheerstelsels. Die doel van hierdie studie is dan om 'n ingebedde beheerder vir 'n AML te ontwikkel en so 'n DSP platform vir navorsing in ingebedde beheerstelsels daar te stel.

Die ingebedde beheerder wat gedurende hierdie studie ontwikkel word moet daartoe in staat wees om 'n spil met 'n rotasiespoed van 60 000 opm aktief te beheer. Dit moet verder daartoe in staat wees om selfstandig bedryf te word, skaleerbaar te wees in terme van die aantal asse wat beheer word en aanpasbaar wees in terme van die beheeralgoritme implementering.

'n TMS320F2812 DSP is gekies op grond van die verwerkingspoed, ingebedde randapparatuur en die ontwikkellingshulpmiddels wat daarvoor beskikbaar is soos die eZdsp<sup>®</sup> DSP Starter Kit, VisSim<sup>®</sup> Embedded Controls Developer en Code Composer Studio<sup>®</sup>. Die koppelvlak van die ingebedde beheerder is ontwerp vir 'n bestaande dubbel radiale aktiewe magnetiese laer, wat dit moontlik maak om die gedrag van die ingebedde beheerder te vergelyk met die van die bestaande rekenaar-gebasseerde beheerder.

Die AML stelsel toon 'n geringe toename in tweede orde ekwivalente styfheid en demping wanneer die ingebedde beheerder gebruik word in vergelyking met die rekenaar-gebasseerde beheerder. Die AML stelsel is ook 'n bietjie minder sensitief wanneer die ingebedde beheerder gebruik word.

Die ingebedde beheerder slaag in die doel om 'n DSP platform daar te stel vir verdere navorsing in ingebedde beheerstelsels en gevorderde beheeralgoritmes. Die kennis opgedoen tydens hierdie studie dien as noodsaaklike boustene vir die oorkoepelende doel van AML integrasie, deur die progressie van 'n DSP na FPGA en uiteidelik 'n ASIC.

### Acknowledgements

Firstly I would like to thank THRIP and M-Tech Industrial for their sponsorship of this study. Without their support, it would certainly not have been possible.

I would also like to extend my utmost appreciation and thanks to the following people:

- My supervisors, for their guidance and motivation throughout this study.

- My parents, for their unconditional love and support.

- My friend André for proofing this dissertation and much needed coffee breaks.

- My friend Morné for his ideas and meaningful inputs.

- My friends Kenny, Kobus, Markus, Sois and Charl.

This dissertation is typeset with LATEX using the LYX document processor in conjunction with a BibTEX reference library.

Hofstadter's Law:

It always takes longer than you expect, even when you take into account Hofstadter's Law.

- Douglas Hofstadter, Gödel, Escher, Bach, 1979.

# Contents

| Summary |         |               |                           |   |

|---------|---------|---------------|---------------------------|---|

| Oŗ      | osomr   | ning          | ii                        |   |

| Li      | st of H | igures        | xi                        |   |

| Li      | st of T | <b>Tables</b> | xiv                       |   |

| Li      | st of A | Abbevia       | tions xv                  |   |

| Li      | st of S | Symbols       | xvii                      |   |

| 1       | Intr    | oductio       | 1                         |   |

|         | 1.1     | Backg         | round on AMBs             |   |

|         |         | 1.1.1         | Basic operating principle |   |

|         |         | 1.1.2         | Digital control           | , |

|         |         | 1.1.3         | Integration               | I |

|         |         | 1.1.4         | DSP technology            | • |

|   | 1.2  | Proble   | m statement                | 4  |

|---|------|----------|----------------------------|----|

|   | 1.3  | Issues   | to be addressed            | 5  |

|   |      | 1.3.1    | Specification              | 6  |

|   |      | 1.3.2    | Platform selection         | 6  |

|   |      | 1.3.3    | Interfacing                | 6  |

|   |      |          | 1.3.3.1 Input              | 7  |

|   |      |          | 1.3.3.2 Output             | 7  |

|   |      | 1.3.4    | DSP algorithm              | 7  |

|   |      |          | 1.3.4.1 Simulation         | 7  |

|   |      |          | 1.3.4.2 DSP implementation | 8  |

|   |      | 1.3.5    | System verification        | 8  |

|   | 1.4  | Disser   | tation overview            | 8  |

| 2 | Lite | rature S | Study                      | 10 |

|   |      |          |                            |    |

|   | 2.1  | A digit  | tal AMB control system     | 10 |

|   | 2.2  | Analog   | gue to digital conversion  | 11 |

|   |      | 2.2.1    | Amplitude                  | 12 |

|   |      | 2.2.2    | Frequency content          | 13 |

|   | 2.3  | Digital  | l to analogue conversion   | 16 |

|   | 2.4  | Proces   | sor concerns               | 17 |

|   |      | 2.4.1    | The control law            | 18 |

|   |                                               | 2.4.2                                 | Sampling rate                                                                                                                                        | 20                                                                                                         |

|---|-----------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|   |                                               | 2.4.3                                 | Number representation                                                                                                                                | 20                                                                                                         |

|   | 2.5                                           | Interfa                               | ce filters                                                                                                                                           | 21                                                                                                         |

|   |                                               | 2.5.1                                 | Filter transfer function                                                                                                                             | 22                                                                                                         |

|   |                                               |                                       | 2.5.1.1 Elliptic                                                                                                                                     | 22                                                                                                         |

|   |                                               |                                       | 2.5.1.2 Chebyshev                                                                                                                                    | 24                                                                                                         |

|   |                                               |                                       | 2.5.1.3 Butterworth                                                                                                                                  | 26                                                                                                         |

|   |                                               |                                       | 2.5.1.4 Bessel                                                                                                                                       | 28                                                                                                         |

|   |                                               | 2.5.2                                 | Impact on AMB performance                                                                                                                            | 29                                                                                                         |

|   | 2.6                                           | Conclu                                | usion                                                                                                                                                | 30                                                                                                         |

|   |                                               |                                       |                                                                                                                                                      |                                                                                                            |

| 3 | Syst                                          | em Desi                               | ign                                                                                                                                                  | 31                                                                                                         |

| 3 | <b>Syst</b><br>3.1                            |                                       | ign                                                                                                                                                  |                                                                                                            |

| 3 | •                                             | Design                                |                                                                                                                                                      | 31                                                                                                         |

| 3 | 3.1                                           | Design<br>Systen                      | process                                                                                                                                              | 31<br>33                                                                                                   |

| 3 | 3.1<br>3.2                                    | Design<br>System<br>DSP p             | n process                                                                                                                                            | 31<br>33<br>35                                                                                             |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Design<br>System<br>DSP p             | n process                                                                                                                                            | <ul><li>31</li><li>33</li><li>35</li><li>38</li></ul>                                                      |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Design<br>Systen<br>DSP pl<br>Interfa | n process                                                                                                                                            | <ul> <li>31</li> <li>33</li> <li>35</li> <li>38</li> <li>39</li> </ul>                                     |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Design<br>Systen<br>DSP pl<br>Interfa | a process                                                                                                                                            | <ul> <li>31</li> <li>33</li> <li>35</li> <li>38</li> <li>39</li> </ul>                                     |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Design<br>Systen<br>DSP pl<br>Interfa | a process   an specification   latform selection   latform selection   ace design   AMB interface   3.4.1.1   Power amplifier synchronisation output | <ul> <li>31</li> <li>33</li> <li>35</li> <li>38</li> <li>39</li> <li>39</li> <li>39</li> <li>39</li> </ul> |

|   |      | 3.4.3   | User interface                                                                                              | 46 |

|---|------|---------|-------------------------------------------------------------------------------------------------------------|----|

|   |      | 3.4.4   | Mains interface                                                                                             | 50 |

|   | 3.5  | DSP fi  | mware                                                                                                       | 50 |

|   | 3.6  | Simula  | tion                                                                                                        | 50 |

|   |      | 3.6.1   | VisSim <sup>®</sup> simulation model verification $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 51 |

|   |      | 3.6.2   | Interface filters                                                                                           | 51 |

|   |      | 3.6.3   | DSP firmware                                                                                                | 53 |

|   | 3.7  | Conclu  | sion                                                                                                        | 54 |

| 4 | Desi | on impl | ementation                                                                                                  | 55 |

| • | Degi | -       |                                                                                                             |    |

|   | 4.1  | Interfa | ce implementation                                                                                           | 55 |

|   |      | 4.1.1   | AMB interface                                                                                               | 55 |

|   |      |         | 4.1.1.1 Power amplifier synchronisation output                                                              | 55 |

|   |      |         | 4.1.1.2 Current reference output                                                                            | 57 |

|   |      |         | 4.1.1.3 Position reference input                                                                            | 57 |

|   |      | 4.1.2   | PC interface                                                                                                | 59 |

|   |      | 4.1.3   | User interface                                                                                              | 62 |

|   |      | 4.1.4   | Mains interface                                                                                             | 64 |

|   | 4.2  | System  | n integration                                                                                               | 65 |

|   | 4.3  | DSP fi  | rmware implementation                                                                                       | 65 |

|   |      | 4.3.1   | CPU timer                                                                                                   | 70 |

# **Declaration**

I hereby declare that all the material incorporated in this dissertation is my own original unaided work except where specific reference is made by name or in the form of a numbered reference. The work herein has not been submitted for a degree at another university.

|   |      | 4.3.2   | General purpose input/output                   | 70 |

|---|------|---------|------------------------------------------------|----|

|   |      | 4.3.3   | Event manager                                  | 70 |

|   |      | 4.3.4   | ADC                                            | 70 |

|   |      | 4.3.5   | SPI                                            | 71 |

|   |      | 4.3.6   | External interrupt                             | 71 |

|   | 4.4  | Conclu  | ision                                          | 72 |

| 5 | Syst | em veri | fication                                       | 73 |

|   | 5.1  | Interfa | ce verification                                | 73 |

|   |      | 5.1.1   | AMB interface                                  | 73 |

|   |      |         | 5.1.1.1 Power amplifier synchronisation output | 73 |

|   |      |         | 5.1.1.2 Current reference output               | 74 |

|   |      |         | 5.1.1.3 Position reference input               | 76 |

|   |      | 5.1.2   | PC interface                                   | 76 |

|   | 5.2  | Firmw   | are execution verification                     | 78 |

|   | 5.3  | Overal  | l system verification                          | 78 |

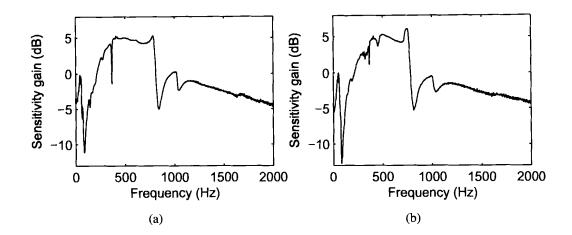

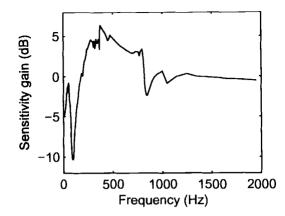

|   |      | 5.3.1   | System sensitivity                             | 79 |

|   |      | 5.3.2   | Static stiffness                               | 80 |

|   |      | 5.3.3   | Equivalent stiffness and damping               | 81 |

|   | 5.4  | Conclu  | ision                                          | 84 |

ix

| 6  | Con                   | Conclusion 8                |    |  |  |  |

|----|-----------------------|-----------------------------|----|--|--|--|

|    | 6.1                   | Development tools           | 85 |  |  |  |

|    | 6.2                   | Interfacing                 | 86 |  |  |  |

|    | 6.3                   | Firmware implementation     | 86 |  |  |  |

|    | 6.4                   | Future work                 | 87 |  |  |  |

|    |                       | 6.4.1 Simulation refinement | 87 |  |  |  |

|    |                       | 6.4.2 Interfacing           | 88 |  |  |  |

|    |                       | 6.4.3 Firmware              | 89 |  |  |  |

|    | 6.5                   | Conclusion                  | 89 |  |  |  |

| Re | eferen                | ces                         | 90 |  |  |  |

| Aŗ | Appendix              |                             |    |  |  |  |

| A  | Contents of data CD 9 |                             |    |  |  |  |

# **List of Figures**

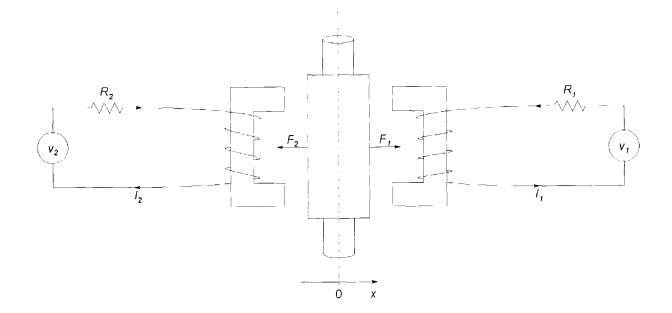

| 1.1 | A simple 1 DOF AMB [3]                       | 2  |

|-----|----------------------------------------------|----|

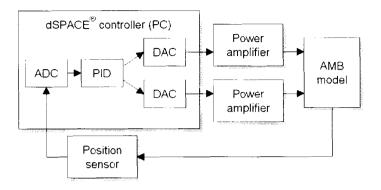

| 1.2 | Current PC-based AMB controller              | 3  |

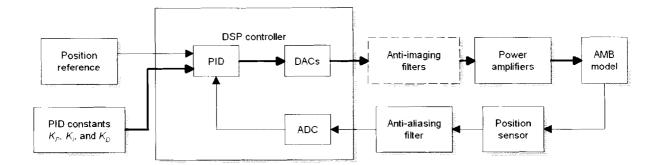

| 1.3 | Embedded AMB controller                      | 5  |

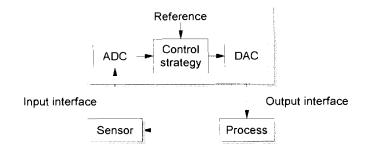

| 2.1 | A simple digital control system              | 11 |

| 2.2 | Quantisation of an ideal 3-bit ADC           | 12 |

| 2.3 | Aliasing caused by undersampling             | 14 |

| 2.4 | Synchronous sampling                         | 15 |

| 2.5 | DAC conversion                               | 16 |

| 2.6 | Analogue signal reconstruction               | 17 |

| 2.7 | PID signal flow [19]                         | 19 |

| 2.8 | 3D direct second order filter structure [19] | 20 |

| 2.9 | Analogue filter responses                    | 23 |

| 0.4 |                                              | 20 |

| 3.1 | Controller design process                    | 52 |

| 3.2 | System interfaces                            | 34 |

| 3.3  | TMS320F2812 eZdsp® DSK [25]                                | 38 |

|------|------------------------------------------------------------|----|

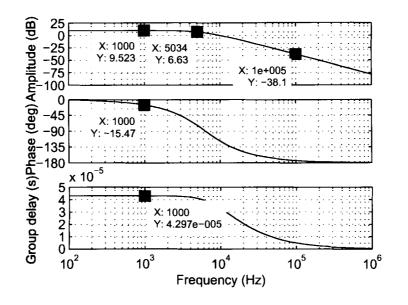

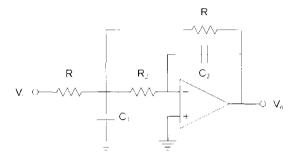

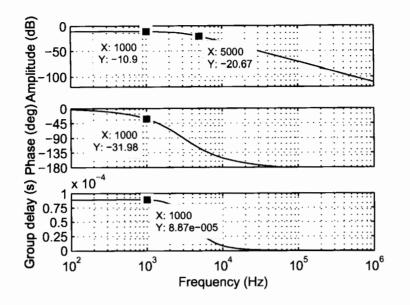

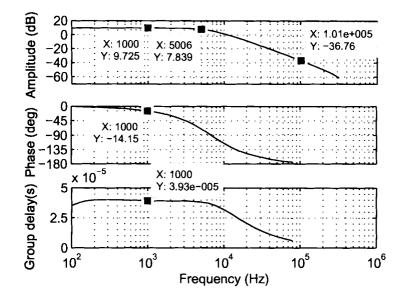

| 3.4  | AIF frequency response                                     | 40 |

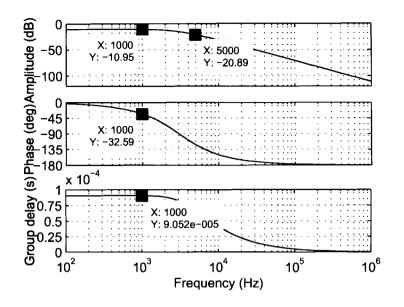

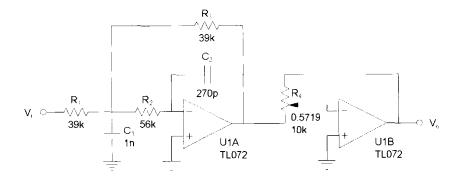

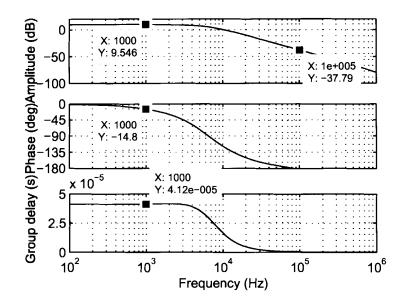

| 3.5  | AAF frequency response                                     | 43 |

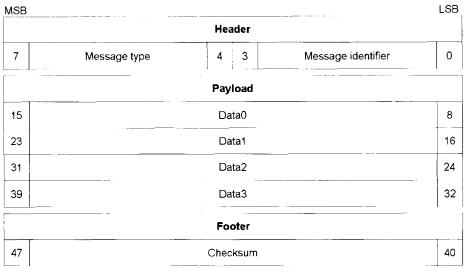

| 3.6  | Packet frame definition                                    | 45 |

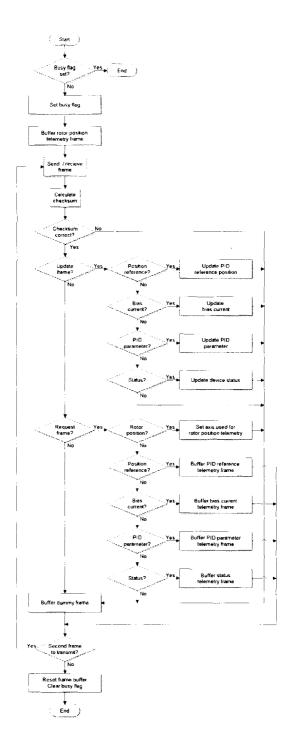

| 3.7  | Protocol flow diagram: Master                              | 48 |

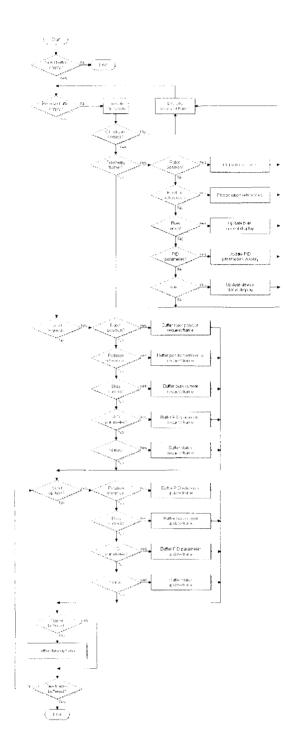

| 3.8  | Protocol flow diagram: Slave                               | 49 |

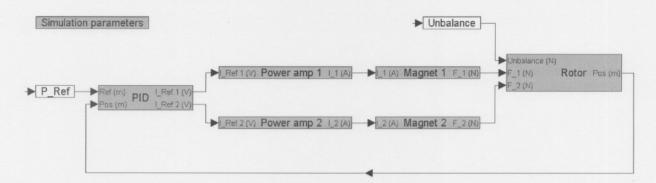

| 3.9  | Base VisSim <sup>®</sup> model                             | 51 |

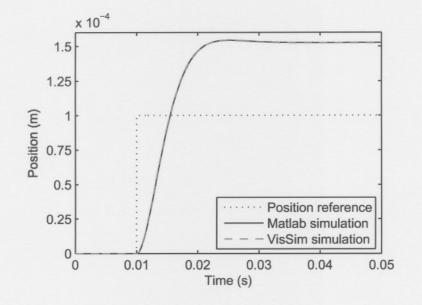

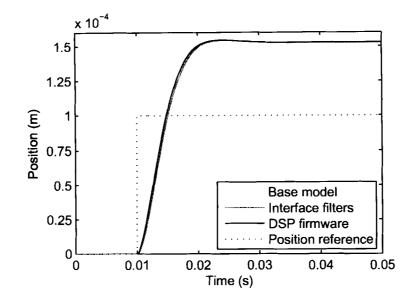

| 3.10 | VisSim <sup>®</sup> model verification                     | 52 |

| 3.11 | Interface simulation model                                 | 52 |

| 3.12 | Interface filter and DSP firmware simulations              | 53 |

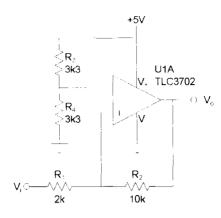

| 4.1  | 5 V Buffer circuit                                         | 56 |

| 4.2  | 5 V Buffer simulation                                      | 56 |

| 4.3  | Multiple feedback circuit [34]                             | 57 |

| 4.4  | Anti-imaging filter circuit                                | 58 |

| 4.5  | Anti-imaging filter simulation                             | 58 |

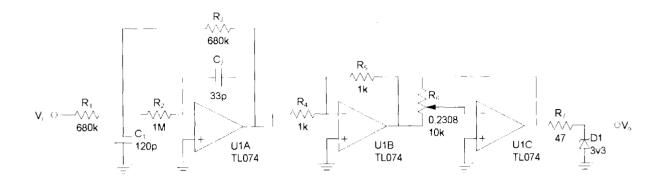

| 4.6  | Anti-aliasing filter circuit                               | 59 |

| 4.7  | Anti-aliasing filter simulation                            | 60 |

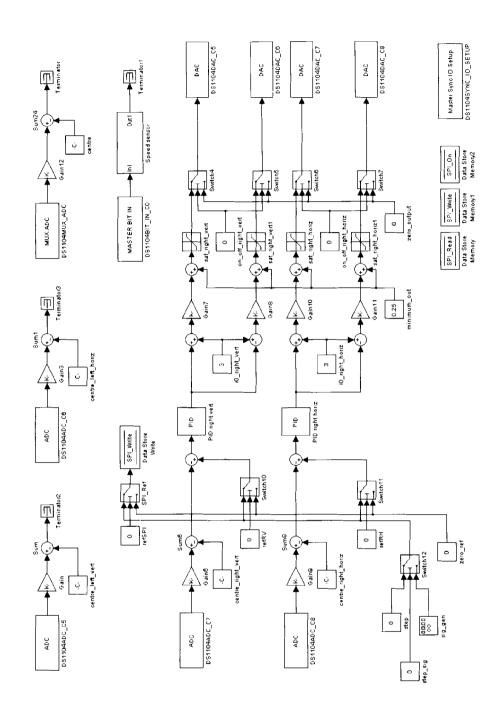

| 4.8  | dSpace <sup>®</sup> controller Simulink <sup>®</sup> model | 61 |

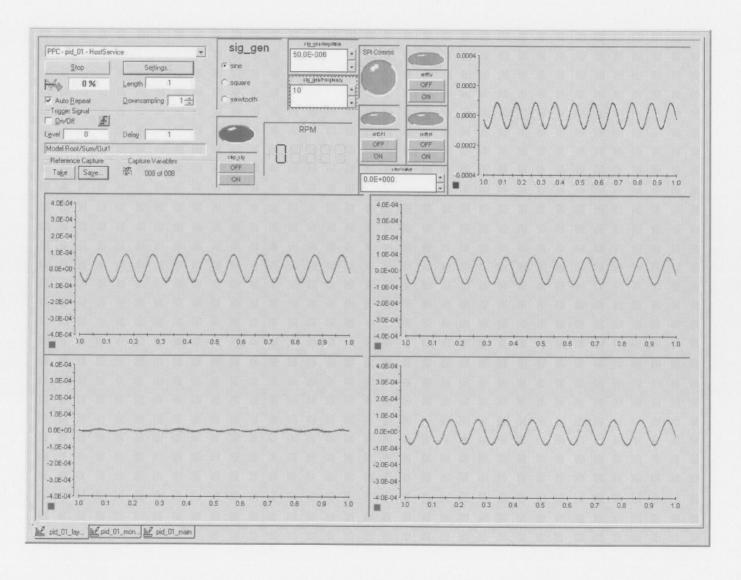

| 4.9  | ControlDesk <sup>®</sup> data capture window               | 63 |

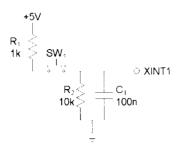

| 4.10 | Pushbutton circuit                                         | 64 |

#### LIST OF FIGURES

#### LIST OF FIGURES

| 4.11 | System integration                                                                | 66 |

|------|-----------------------------------------------------------------------------------|----|

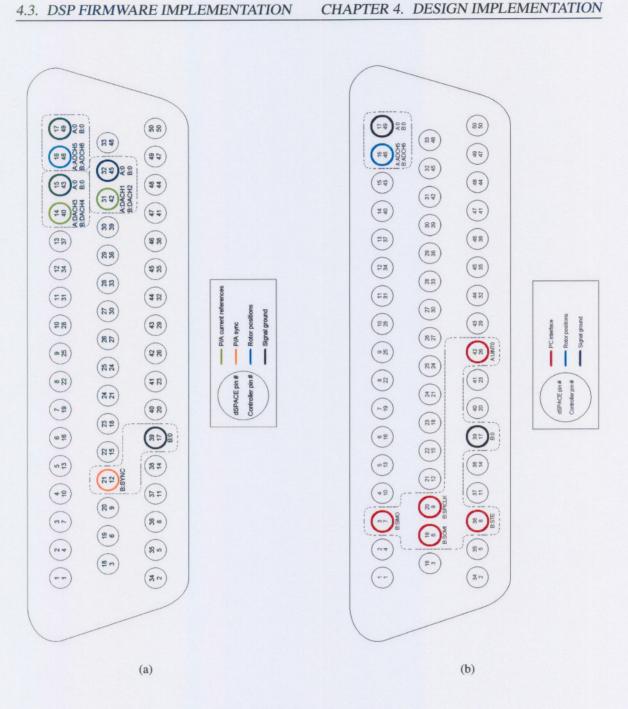

| 4.12 | System connectors                                                                 | 67 |

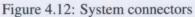

| 4.13 | Photograph of embedded controller                                                 | 68 |

| 4.14 | Signal scaling                                                                    | 69 |

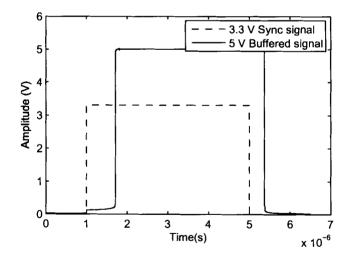

| 5.1  | Power amplifier synchronisation output                                            | 74 |

| 5.2  | Anti-imaging filter response                                                      | 75 |

| 5.3  | Anti-aliasing filter response                                                     | 76 |

| 5.4  | Round-trip time measurement                                                       | 77 |

| 5.5  | Firmware execution measurement                                                    | 78 |

| 5.6  | Sensitivity gain measurement                                                      | 79 |

| 5.7  | Embedded controller system sensitivity                                            | 80 |

| 5.8  | dSPACE® controller sensitivity - Left horizontal                                  | 81 |

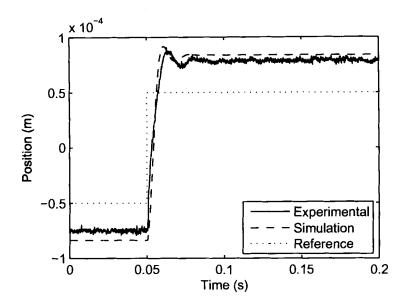

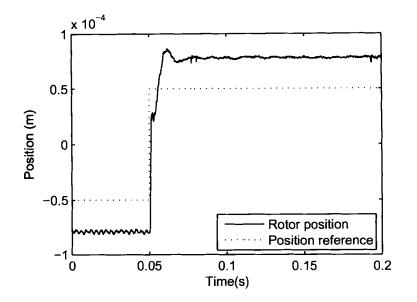

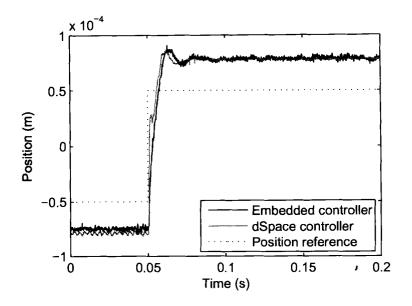

| 5.9  | Embedded controller 100 $\mu$ m horizontal step                                   | 82 |

| 5.10 | dSPACE <sup>®</sup> controller 100 $\mu$ m horizontal step                        | 84 |

| 6.1  | 100 $\mu$ m step response, embedded controller and dSPACE <sup>®</sup> controller | 87 |

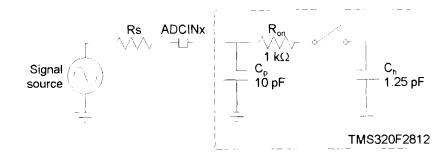

| 6.2  | ADC analogue input impedance model [24]                                           | 88 |

# **List of Tables**

| 2.1 | Filter specifications                                                                          | 22         |

|-----|------------------------------------------------------------------------------------------------|------------|

| 2.2 | Normalised elliptic loss functions for $A_{max} = 0.5 \text{ dB} [21] \dots \dots \dots \dots$ | 25         |

| 3.1 | System specification                                                                           | 36         |

| 3.2 | Message type definition                                                                        | 46         |

| 3.3 | Message identifier definition                                                                  | 47         |

| 5.1 | Anti-imaging filter realisation                                                                | 75         |

| 5.2 | Anti-aliasing filter realisation                                                               | <b>7</b> 7 |

# **List of Abbreviations**

| AAF  | Anti-Aliasing Filter                    |

|------|-----------------------------------------|

| AC   | Alternating Current                     |

| ADC  | Analogue to Digital Converter           |

| AIF  | Anti-Imaging Filter                     |

| AMB  | Active Magnetic Bearing                 |

| ASIC | Application Specific Integrated Circuit |

| CMOS | Complementary Metal Oxide Semiconductor |

| DAC  | Digital to Analogue Converter           |

| DC   | Direct Current                          |

| DOF  | Dergree Of Freedom                      |

| DSP  | Digital Signal Processor / Processing   |

| EMC  | Electromagnetic Compatability           |

| ESD  | Electrostatic Discharge                 |

| FIFO | First In First Out                      |

| FPGA | Field Programmable Gate Array           |

| GPIO | General Purpose Input/Output            |

| I/O  | Input/Output                            |

| LED  | Light-Emitting Diode                    |

| LSB         | Least Significant Bit                        |

|-------------|----------------------------------------------|

| MFLOPS      | Million Floating Point Operations Per Second |

| MIPS        | Million Instructions Per Second              |

| Mbps        | Mega bits per second                         |

| Msps        | Mega samples per second                      |

| PC          | Personal Computer                            |

| PID         | Proportional-Integral-Derivative             |

| PWM         | Pulse Width Modulation                       |

| RAM         | Random Access Memory                         |

| <b>rp</b> m | Revolutions per minute                       |

| SPI         | Serial Peripheral Interface                  |

| TTL         | Transistor-Transistor Logic                  |

| XINT        | External Interrupt                           |

| ZOH         | Zero-Order Hold                              |

xvi

# **List of Symbols**

| $A_{max}$       | Maximum passband attenuation (dB)         |

|-----------------|-------------------------------------------|

| $A_{min}$       | Minimum stopband attenuation (dB)         |

| $b_{eq}$        | Second order equivalent damping (Ns/m)    |

| $f_a$           | Signal bandwidth (Hz)                     |

| $f_s$           | Sampling frequency (Hz)                   |

| FS              | ADC full scale converted code             |

| $K_d$           | PID derivative gain                       |

| $k_{eq}$        | Second order equivalent stiffness (N/m)   |

| $K_i$           | PID integral gain                         |

| $K_p$           | PID proportional gain                     |

| PO              | Percentage overshoot                      |

| T               | Sampling period (s)                       |

| $T_d$           | Damped oscillation period (s)             |

| $V_{in}$        | Input voltage                             |

| $V_{in_{max}}$  | Maximum input voltage                     |

| $V_{out}$       | Output voltage                            |

| $V_{out_{max}}$ | Maximum output voltage                    |

| $\omega_d$      | Damped oscillation frequency (rad/s)      |

| $\omega_P$      | Passband frequency (rad/s)                |

| $\omega_n$      | Natural frequency (rad/s)                 |

| $\omega_S$      | Stopband frequency (rad/s)                |

| $\omega_{wp}$   | PID differentiator pole frequency (rad/s) |

|                 |                                           |

### **Chapter 1**

### Introduction

This chapter provides some basic information on the operation of AMBs, as well as some introductory information on digital control and the motivation behind an embedded controller for active magnetic bearings. It also includes the problem statement and a description of the research method to be followed.

#### 1.1 Background on AMBs

Active magnetic bearings are used by industry to suspend high-speed rotating machines. Applications of AMBs range from energy storage flywheels to high-speed spindles and turbo machinery. AMBs are primarily used for these applications because of their contact free operation. AMBs are further capable of dynamically adjusting their characteristics such as the stiffness and damping.

#### **1.1.1 Basic operating principle**

Active magnetic bearings operate on the principle that an attraction force is generated in the air gap of an electromagnet. The force attempts to reduce the reluctance by closing the air gap and is nonlinear in nature [1]. Closed-loop control is therefore needed to realise stable, contact free suspension of the rotor in mid-air.

1

Figure 1.1: A simple 1 DOF AMB [3]

A simple one degree of freedom AMB is shown in Figure 1.1 in order to demonstrate the use of the electromagnets. By using two electromagnets opposing each other, the AMB is capable of producing both positive and negative forces on the rotor. This enables the force of the AMB to be linearised if the magnets are operated in differential mode [2] and improves the controllability of the AMB.

#### 1.1.2 Digital control

Traditionally, AMBs were controlled by means of analogue PID controllers. These controllers had to be tuned for each application [4]. Digital control is now possible through advances in DSP technology, facilitating the implementation of advanced control methods that are more flexible, as some algorithms can even incorporate on-line training [5].

Digital controllers have various advantages. They enable designers to implement flexible control systems with optimal control strategies in order to obtain a higher stiffness than was previously achievable with analogue PID controllers [6].

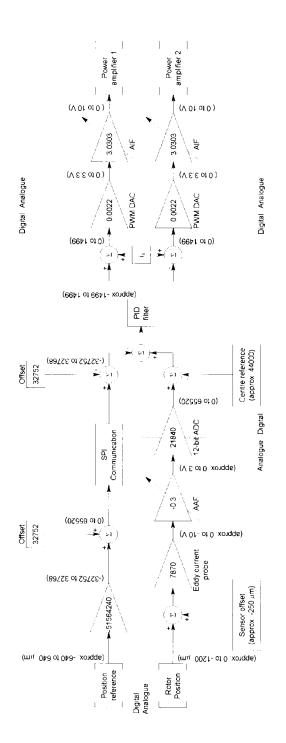

Figure 1.2: Current PC-based AMB controller

By implementing digital controllers even the non-linearity of the system can be compensated for. The force of the magnetic bearing can thus be linearised over virtually the entire working range of the AMB, without using large bias currents [7].

Digital controllers have also realised the possibility of condition monitoring. The AMB can then diagnose the entire rotor's integrity as well as the integrity of the bearing itself [8].

#### 1.1.3 Integration

Digital control is currently implemented with component-based systems [9]. The AMB and the controller are therefore two separate units. An example of this is the existing double radial AMB model in the School for Electrical, Electronic and Computer Engineering at North-West University [10]. Figure 1.2 shows a block diagram of the PC-based controller which utilises a dSPACE<sup>®</sup> expansion card. The expansion card includes an on-board DSP as well as multiple digital and analogue inputs and outputs. The controller's software is generated using Matlab<sup>®</sup> Simulink<sup>®</sup>, which simplifies code development. Although the controller is very versatile, it is also a expensive piece of equipment.

Greater integration will enable AMBs to be more flexible in their application and will therefore expand the use of AMBs. Implementing an embedded control system using a DSP-based controller is the first step to a higher level of integration [7].

#### 1.1.4 DSP technology

DSP technology has now evolved to such a point that it can be used to implement complex motor control algorithms within a graphical programming language [11]. This enables the developer to develop complex, optimised, reliable DSP code without an extensive knowledge of assembler or even C programming.

Research into this field is therefore necessary to establish expertise in the field of DSP which will aid in the development of an integrated active magnetic bearing.

#### **1.2 Problem statement**

The purpose of the study is to realise an experimental development model of a controller with the following functionality for AMB control applications:

- 1. Embedded DSP-based implementation

- 2. Standalone operation

- 3. Scalable platform in terms of the number of axes to be controlled

- 4. Flexible in terms of the control algorithm used and specific application

- 5. High bandwidth

- 6. Capable of implementing additional functions such as condition monitoring

There are two specific applications for which the embedded controller is earmarked, the first being the implementation of the current PID control algorithm on the double radial AMB model. Secondly, the controller should also be capable of accurately controlling other high-speed AMBs such as high-speed spindles. The major difference between the mentioned applications, are the required bandwidth. For the double radial AMB model, the system will need to actively control disturbances with a maximum frequency of 500 Hz, while the system will need to actively control disturbances with a maximum frequency of 1 kHz for the high-speed spindle.

Figure 1.3: Embedded AMB controller

The embedded controller will thus greatly contribute to the AMB research infrastructure of the School for Electrical, Electronic and Computer Engineering and plays a crucial role in future high-speed AMB development.

#### **1.3** Issues to be addressed and methodology

The first step in developing the embedded controller is compiling a detailed specification, listing all the relevant requirements and constraints of the controller. The appropriate DSP platform, chip, development board and programming environment can then to be selected. Once this is done, the interfacing requirements between the current model and embedded controller can be investigated and satisfied.

A block diagram of the embedded controller is shown in Figure 1.3. It shows the anti-aliasing filter used to bandwidth-limit the input signal, as well as an anti-imaging filters which can be used to bandwidth-limit reference signals for the power amplifiers if necessary. An AMB's transfer function is inherently low-pass in nature, which usually makes the use of an anti-imaging filter unnecessary [2].

The interface circuits have to scale the signals to the appropriate ranges in order to maximise the resolution of the signals and enable the controller to interface with the double radial AMB model. The transfer characteristics of the input and output circuits have to be verified before implementing them in the AMB model.

Once the embedded controller can be safely interfaced with the double radial AMB model, the existing PID control algorithm can be implemented using the chosen development environment and compiled for the chosen DSP chip. The computational requirements of the control algorithm can then be determined. When the embedded controller is fully integrated, the performance of the system can practically be verified.

Each of the mentioned aspects are now discussed in detail.

#### 1.3.1 Specification

Firstly the relevant requirements and constraints of the embedded controller are specified, including required system bandwidth. This specification will be used to evaluate the successful implementation of the controller.

#### **1.3.2** Platform selection

The appropriate DSP platform is selected with the specifications in mind. This is done by selecting the appropriate DSP manufacturer, DSP series, DSP chip, development board and programming environment.

For DSP selection, processing speed, word length, peripherals, cost and availability has to be considered. In selecting the programming environment, cost, availability, features and ease of integration have to be evaluated while keeping the selected DSP development board in mind. The selected hardware and software is then sourced.

#### 1.3.3 Interfacing

Both the input and output interfacing requirements need to be considered. Each is subsequently discussed.

#### 1.3.3.1 Input

As previously stated, the DSP must be safely interfaced with the position sensors of the double radial AMB model. This is accomplished by scaling the input signals to match the full scale of the DSP's A/D converter in order to minimise the effect of quantisation errors. The DSP also needs to be protected from over-voltage and ESD phenomena.

Further, the input from the position sensors have to be band-limited in order to prevent aliasing. This is accomplished by designing the filter so as to provide adequate attenuation at the Nyquist frequency. The filter also cannot distort the control signal.

#### 1.3.3.2 Output

The double radial AMB model's power amplifiers are designed to generate their own PWM signal and need only a current reference from the controller. The selected DSP therefore has to incorporate an DAC to generate the necessary current reference. As various motor-control DSPs do not incorporate DACs, it should also be considered to low-pass filter a PWM output of the DSP, which would therefore necessitate the use of an anti-imaging filter.

Further, the output has to be scaled to match the current reference levels expected by the power amplifiers.

#### **1.3.4 DSP algorithm**

The next step would be to implement the existing control algorithm on the embedded controller. This has to be done by firstly verifying the AMB's dynamic performance by simulation and finally implementing the control algorithm on the DSP itself.

#### 1.3.4.1 Simulation

In order to verify the influence of the filters on the control algorithm, the AMB must first be simulated with the analogue filters, ADC, DAC, etc. implemented in software. Upon successful verification of the system's dynamic performance, the control algorithm can be implemented.

#### 1.3.4.2 DSP implementation

After successful simulation, the control algorithm can be implemented on the embedded controller with relative ease. Once the control algorithm is implemented on the DSP, the performance of the AMB system can be verified.

#### **1.3.5** System verification

The verification of the system should be done incrementally. Firstly, the transfer characteristics of the interface should be verifed before the embedded controller is intergrated. If the transfer characteristics are acceptable, the embedded controller can be integrated.

If the embedded controller has been fully integrated, the closed-loop system performance of the embedded controller can be verifed by determining the system sensitivity, as well as the second order equivalent stiffness and damping.

#### **1.4 Dissertation overview**

Chapter 2 contains a detailed literature study on the aspects involved in designing a digital control system. It starts off with a discussion of digital control systems in general and proceeds to focus on digitally controlled AMBs specifically. It then discusses various issues regarding analogue to digital conversion, digital to analogue conversion, controller cycle time, digital number representation and filter selection.

In Chapter 3, a detailed description of the embedded controller's design is given. It starts off with a discussion of the design process followed and then discusses the system specification. Hereafter the DSP platform and development tools are selected. The system interfaces are then designed and the AMB system is simulated in its entirety.

The design implementation is discussed in Chapter 4, starting with a description of the interface implementation. The DSP firmware implementation is also discussed in detail.

The overall system performance is evaluated in Chapter 5 by verifying the interface characteristics and analysing the system's sensitivity and step response. From the step response, the equivalent second order stiffness and damping are determined. The system performance in also compared to the existing dSPACE<sup>®</sup> controller.

Chapter 6 gives a critical account of the insights gained during the development of the embedded controller. It discusses aspects such as interfacing and firmware implementation. Some ares are then identified which require further investigation.

### Chapter 2

### **Literature Study**

This chapter covers various issues regarding digital control systems. It starts off with a basic, generic digital control system and then discusses issues regarding analogue to digital conversion, digital to analogue conversion, the processor itself and concludes with a section on filter selection.

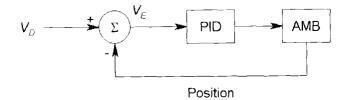

#### 2.1 A digital AMB control system

A basic, generic digital control system consists of an analogue to digital converter (ADC), a digital processor, a digital to analogue converter (DAC) and a feedback sensor, as depicted in Figure 2.1. The ADC converts the analogue output of the feedback sensor into a digital format which can be used by the digital processor. The processor compares the desired (reference) state of the process to the actual state, as converted by the ADC. It then determines the action required to bring the process to the desired state, according to the control strategy used. This action is then communicated to the process using the DAC and the result is measured by the feedback sensor.

An AMB system is no different to the generic control system described above, although it imposes some unique requirements. Usually the time constant of a plant is relatively long, so the control system is not affected by the time delays imposed by the controller. An AMB system, on the other hand, is very sensitive to time delays in the control loop [2, 12]. In some instances, even a time delay of 120  $\mu$ s cannot be tolerated. The AMB system is therefore classified as a real-time system.

٧

Figure 2.1: A simple digital control system

In order to successfully implement a digital control system, the following aspects have to be considered carefully [2]:

- Analogue to digital conversion,

- Digital to analogue conversion,

- The control law,

- Sampling rate, and

- Number representation within the processor.

Analogue to digital conversion and digital to analogue conversion are discussed separately in the following sections. This is followed by a discussion of the control law, sampling rate, and number representation in the section covering processor concerns.

#### 2.2 Analogue to digital conversion

When an analogue signal is to be converted into a digital, sampled signal, it is important to consider the impact the conversion will have on both the amplitude and frequency content of the signal [13]. This determines the signal conditioning necessary at the input interface and determines the accuracy to be expected of the analogue to digital conversion process.

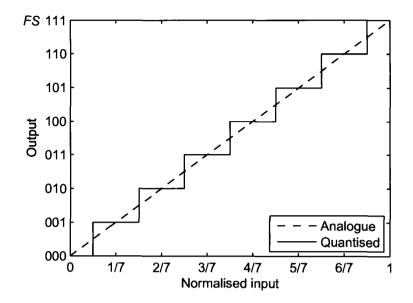

Figure 2.2: Quantisation of an ideal 3-bit ADC

#### 2.2.1 Amplitude

In order to illustrate the effect of analogue to digital conversion on the amplitude of the signal, the output of an ideal 3-bit unipolar ADC is shown in Figure 2.2. An ideal unipolar ADC makes it first transition at  $\frac{1}{2}$  LSB and at every LSB after that until it has reached full scale (*FS*). This causes a quantisation error of maximum  $\frac{1}{2}$  LSB [13].

In an AMB system, the  $\frac{1}{2}$  LSB error is usually negligible when a 12-bit ADC is used. However, the error is amplified if the converted signal's voltage range does not match the ADC's voltage range. It is therefore important to match the maximum input voltage to the FS voltage of the ADC [2].

There are four types of DC errors which could also severely increase the quantisation error; each discussed in turn in the following paragraphs [13, 14].

**Gain error:** The gain error causes the real converted value to be a constant times the ideal converted value if it is the only error which occurs.

**Offset error:** The offset error causes the real converted value and ideal converted value to differ by a constant value if it is the only error which occurs.

**Integral linearity error:** The integral linearity error is analogous to the linearity error of an amplifier. It occurs as the real transfer characteristic of the ADC differs from a straight line.

**Differential nonlinearity error:** The differential nonlinearity error relates to the linearity of the code transitions of the ADC. This type of error occurs when a change of 1 LSB in the analogue signal causes the converted value to stay the same, to skip a code or even to go back to a smaller code.

The gain and offset errors can be alleviated by the user through compensation in the DSP software, but the integral linearity and differential nonlinearity errors are intrinsic to the ADC and should be specified by the manufacturer as it determines the performance that can be expected from the ADC [13].

#### 2.2.2 Frequency content

The effect of analogue to digital conversion on the frequency content of the signal is now considered. In this section it is assumed that no quantisation errors occur. Suppose an analogue signal has a bandwidth of  $f_a$ , having no frequency component higher than  $f_a$ , and is sampled at a frequency of  $f_s$ . According to the Nyquist sampling theorem [15], all the information within the signal can only be preserved if

$$f_s \ge 2 \times f_a \tag{2.1}$$

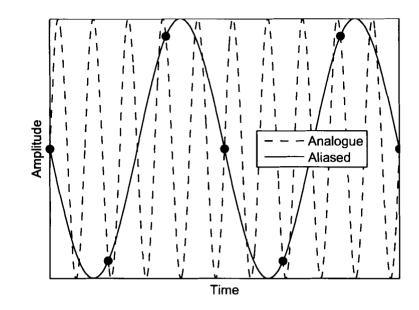

An effect called aliasing occurs if the signal is sampled at a frequency  $f_s$  with  $f_s < 2 \times f_a$ , as shown in Figure 2.3. From the figure it can be seen that the high-frequency signal is now perceived to be a signal with a frequency less than  $\frac{f_s}{2}$ . It is therefore necessary to limit the bandwidth of the analogue signal to prevent aliasing. This can be done using a combination of the following approaches, namely:

• Increasing the ADC's sampling rate,

Figure 2.3: Aliasing caused by undersampling

- Synchronous sampling, and

- Analogue filtering.

Increasing the ADC's sampling rate increases the bandwidth of the signal which can be digitised. Sometimes the sampling rate of the ADC can be far greater than  $\frac{f_a}{2}$ . The signal can then be filtered digitally and decimated in time. As the filter output and decimation can take long to compute, this approach can pose a problem in real-time applications like the AMB system and is therefore not considered further [16].

Synchronous sampling can only be used if the frequency components higher than  $\frac{f_s}{2}$  occur at specific intervals, as is illustrated in the following example:

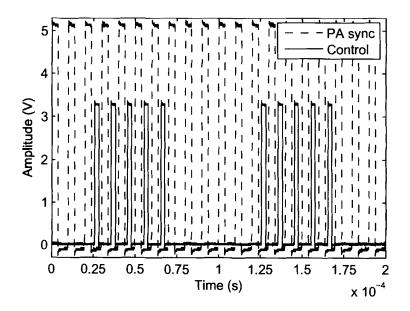

Figure 2.4(a) shows the switching noise of a bi-state power amplifier controlled by a DSP's PWM outputs. The switching noise has a 10 MHz frequency component occurring at a frequency of 100 kHz (the PWM frequency). If the DSP's ADC is used to sample the signal at 20 kHz and the ADC is not synchronised with the PWM, the switching noise will appear as an aliased signal as shown in Figure 2.4(b). If the DSP's ADC is synchronised with the PWM, the ADC can then

Figure 2.4: Synchronous sampling

(a) Signal with 10 MHz noise (b) Asynchronous sampling (c) Synchronous sampling

sample between the occurrences of the switching noise. The effect of the switching noise is then effectively eliminated in the time domain as seen in Figure 2.4(c).

Whenever aliasing signal components occur randomly in time, the only way to proceed is to eliminate them in the frequency domain. This is done by analogue low-pass or band-pass filtering [17]. Usually, a high-order (8-12 poles) "brick-wall" filter is used, but the group delay of the high-order filter can cause the AMB system to become unstable. A lower-order (1-2 poles) filter, with the same passband as the high-order filter, is then used and some aliasing of the input is tolerated [18]. As there is always a random noise component evident in real-world signals, it is prudent to use

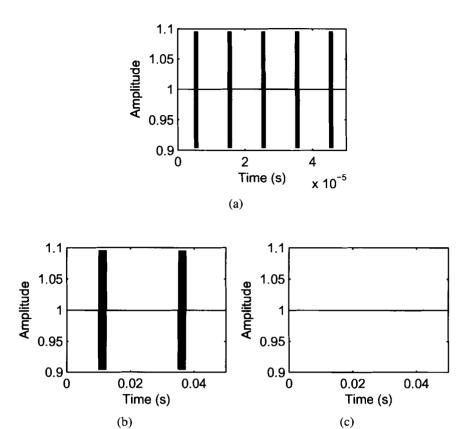

Figure 2.5: DAC conversion

(a) DAC input and output (b) FFT of DAC output

an analogue filter to avoid aliasing, even if a synchronous sampling scheme is used. Analogue low-pass filters are discussed in Section 2.5 as they are relevant to the application concerned.

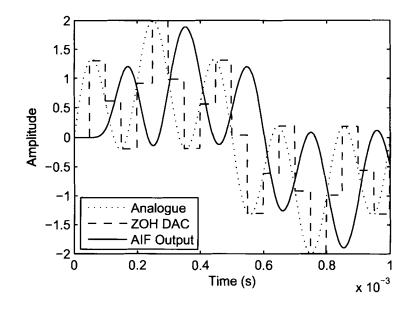

#### 2.3 Digital to analogue conversion

In order to interface with a process, the DSP's digital control signals have to be converted into analogue signals. Figure 2.5(a) shows a signal consisting of 1 kHz and 5 kHz components, both with an amplitude of 1, which is sampled using a zero-order-hold (ZOH) DAC at a rate of 20 kHz. The frequency content of the reconstructed analogue signal is shown in Figure 2.5(b). The amplitude of the frequency components are changed according to (2.2) [13]:

$$H(f) = \left| \frac{\sin\left(\frac{\pi f}{f_s}\right)}{\frac{\pi f}{f_s}} \right|$$

(2.2)

It can also be seen that the frequency components are mirrored and that they repeat at multiples of  $f_s$ . Usually it is necessary to limit the bandwidth of the DAC signal at the output interface by using an analogue low-pass filter, called an Anti-Imaging Filter (AIF), in order to recover the original

Figure 2.6: Analogue signal reconstruction

signal as shown in Figure 2.6. In AMB systems, however, the control plant usually has a low-pass characteristic, making an AIF unnecessary [2].

From Figure 2.6 it can also be seen that the reconstructed analogue signal's amplitude is reduced because of the nature of the DAC signal. This is predicted by (2.2) and seen in Figure 2.5(b). The reconstructed signal is also time delayed due to the filter and ZOH DAC's time delay.

This can have a drastic effect on the behaviour of a closed-loop control system as the high-frequency components are attenuated and introduces a time-delay in the control loop. The amplitude distortion can, however, be corrected by adjusting the AIF's transfer function [15].

# 2.4 Processor concerns

There are mainly three concerns when considering the processor, as mentioned in Section 2.1, namely the control law, sampling rate and number representation within the processor. Each of these is now discussed.

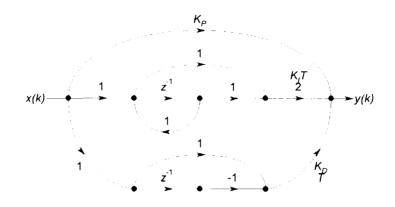

### 2.4.1 The control law

The control law, presumed to be a PID controller for the purpose of this study, has to be converted from a continuous controller into a discrete controller by describing the controller with a set of difference equations [2, 18], written using the z transform in order to integrate and differentiate numerically.

A classical PID controller has the following transfer function [17]:

$$G_c(s) = K_P + \frac{K_I}{s} + K_D s \tag{2.3}$$

where  $K_P$  is the proportional gain,  $K_I$  is the integral gain and  $K_D$  is the derivative gain.

In the w plane the transfer function of the PID control law can also be written as [19]:

$$D(w) = K_P + \frac{K_I}{w} + K_D w \qquad (2.4)$$

The gain of the PID transfer function in (2.4) increases as the frequency increases, which can cause the system to become unstable. This problem is alleviated by introducing a pole  $(\omega_{wp})$ . The transfer function then becomes [19]:

$$D(w) = K_P + \frac{K_I}{w} + \frac{K_D w}{1 + w/\omega_{wp}}$$

(2.5)

If the pole is chosen to be at [19] :

$$\omega_{wp} = -\frac{2}{T} = -\frac{\omega_s}{\pi} \tag{2.6}$$

it is usually far beyond the bandwidth of the system and will have very little impact on the system response. Here  $\omega_s$  is the sampling rate in rad/s and T is the sampling interval.

The transfer function of the PID controller can then be written as [19]:

$$D(z) = K_P + K_I \frac{T}{2} \left[ \frac{z+1}{z-1} \right] + K_D \left[ \frac{z-1}{Tz} \right]$$

(2.7)

Figure 2.7: PID signal flow [19]

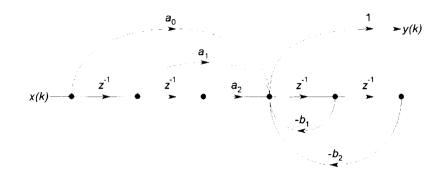

and implemented as shown in Figure 2.7. It may, however, be beneficial to write the transfer function as a standard second-order function. It can then be implemented using one of the standard structures used to realise second-order filters, which will help to avoid coefficient sensitivity problems. If the PID transfer function is written in the form [19]:

$$D(z) = \frac{a_0 + a_1 z^{-1} + a_2 z^{-2}}{1 + b_1 z^{-1} + b_2 z^{-2}}$$

(2.8)

then

$$a_{0} = K_{P} + \frac{K_{I}T}{2} + \frac{K_{D}}{T}$$

$$a_{1} = -K_{P} + \frac{K_{I}T}{2} - \frac{2K_{D}}{T}$$

$$a_{2} = \frac{K_{D}}{T}$$

$$b_{1} = -1$$

$$b_{2} = 0$$

(2.9)

One of the structures with the least amount of operations needed to implement the transfer function is the 3D direct second order filter structure shown in Figure 2.8. Its structure prohibits the unbounded escalation of the node values, which therefore makes it ideal for fixed-point implementation.

Figure 2.8: 3D direct second order filter structure [19]

## 2.4.2 Sampling rate

For digital control systems, it is assumed that the control loop is executed once for every sample. The sampling rate therefore determines the rate at which the input is sampled and the rate at which the output is updated.

The selection of the sampling rate depends on the time constant of the system, and should as a rule of thumb be chosen so that there are at least five samples per time constant [2, 18, 19]. If the sampling rate is chosen too high, the calculated derivatives could have a considerable error, which would make the control system susceptible to noise. If it is chosen too low, the control system would be incapable of actively controlling high-frequency disturbances [2].

### 2.4.3 Number representation

Numbers within digital systems are stored using a digital code with a finite resolution. The code closest to the number is then used to represent it. This is done in one of two ways, namely [15]:

- Floating Point, and

- Fixed Point.

Floating point numbers are represented by three parts. For 32-bit floating point (single precision) numbers, bits 0 to 22 are used for the mantissa (M), bits 23 to 30 for the exponent (E) and bit 31 for the sign (S). The value of the floating point number (v) can then be determined using (2.10) [15]:

$$v = (-1)^S \times M \times 2^{E - 127} \tag{2.10}$$

keeping in mind that some number codes are reserved for  $\pm \infty$ ,  $\pm 0$  and some other codes, referred to as NANs (Not A Number).

Although the floating point numbers are very good at representing large and small numbers [15], the DSPs capable of floating-point calculations are considerably slower than their fixed-point counterparts. For instance, Texas Instrument's TMS320C6x family of DSPs are capable of up to 8000 MIPS (fixed point), but only up to 1800 MFLOPS (floating point) [20]. Generally, floating-point DSPs also do not have peripherals such as ADCs, DACs and PWM controllers on-chip [20] and therefore need more external peripherals to perform the task of digital control.

Fixed-point numbers lack the precision of floating point numbers, as a bit may be used for the sign, a certain number of bits, called the radix, are then used for the integer part of the number and the rest of the bits are used to represent the fraction part of the number as close as possible. Number range and scaling then becomes part of the design process, complicating algorithm implementation [15].

The precision of the number representation will affect the accuracy of the numerical integration and differentiation used, as both the value and the time-step will have numerical errors. A very short sample time will further compound the error as integration and differentiation are done more regularly [2].

# 2.5 Interface filters

As anti-aliasing and anti-imaging are done using low-pass filters, low-pass filters are discussed in detail in this section. First the different filter approximations are discussed, and then the impact of the filters on the closed-loop control is discussed.

| Parameter                                | Value                   |

|------------------------------------------|-------------------------|

| Passband frequency $(\omega_P)$          | 6283.2 rad/s (1 kHz)    |

| Stopband frequency $(\omega_S)$          | 125663.7 rad/s (20 kHz) |

| Maximum passband attenuation $(A_{max})$ | 0.5 dB                  |

| Minimum stopband attenuation $(A_{min})$ | 80 dB                   |

Table 2.1: Filter specifications

### 2.5.1 Filter transfer function

There are mainly four types of approximations which are used to derive a suitable transfer function for the realisation of low-pass filters, namely [21]:

- Elliptic

- Chebyshev

- Butterworth

- Bessel

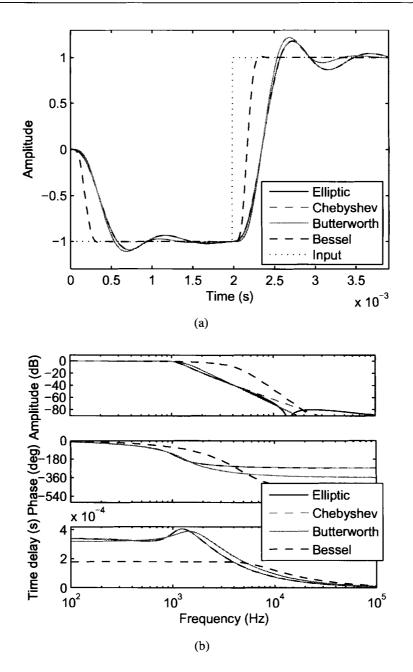

Each approximation uses other criteria, resulting in transfer functions which differ significantly in their amplitude and phase characteristics. A filter is now designed with each of the above mentioned approximations using the specifications given in Table 2.1.

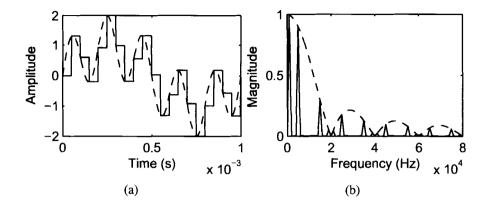

The step and frequency responses of the designed filters is shown in Figures 2.9(a) and (b) respectively.

### 2.5.1.1 Elliptic

The elliptic approximation uses a rational function with finite poles and zeros in order to provide the best possible fit to the loss requirements of the filter. This generally results in the lowest order approximation of all the approximation methods discussed here [21].

Note that the responses of the elliptic and Chebyshev filters are nearly identical.

Figure 2.9: Analogue filter responses

(a) Step response (b) Frequency response

The approximation has distinguishing poles of attenuation in the stopband and equiripple in the passband. The mathematical development of the approximation is quite complex, so the design is done using tabulated normalised transfer functions like those shown in Table 2.2 [21].

In the tables the frequency  $(\Omega)$  is normalised to the passband frequency. Therefore [21]

$$\Omega_S = \frac{\omega_S}{\omega_P} \tag{2.11}$$

The functions are denormalised by replacing [21]

$$s \text{ with } \frac{s}{\omega_P}$$

(2.12)

When a low-pass filter is designed using the elliptic approximation and the specification given in Table 2.1, the filter is a 3rd order filter with the following transfer function:

$$H_F(s) = \frac{22.8018s^2 + 1.5557 \times 10^{-10}s + 1.7797 \times 10^{11}}{(s^3 + 7.8679 \times 10^3 s^2 + 6.0585 \times 10^7 s} + 1.7797 \times 10^{11})$$

(2.13)

#### 2.5.1.2 Chebyshev

The Chebyshev approximation has the aim of attaining the best possible attenuation in the stopband, while allowing a certain amount of equiripple in the passband. The more ripple is allowed, the better attenuation is achieved in the stopband for a given filter order [21].

The loss transfer function of the Chebyshev approximation is described by [21]:

$$|H_L(j\omega)| = \left|\frac{V_{in}(j\omega)}{V_{out}(j\omega)}\right| = \sqrt{1 + \varepsilon^2 C_n^2 \left(\frac{\omega}{\omega_P}\right)}$$

(2.14)

where  $\varepsilon$  is a constant with

$$\varepsilon = \sqrt{10^{0.1A_{max}} - 1} \tag{2.15}$$

| $\Omega_S = 1$ | .5 |

|----------------|----|

|----------------|----|

|   | Denominator |                                   |                                                                     | $A_{min}$     |

|---|-------------|-----------------------------------|---------------------------------------------------------------------|---------------|

| n | Constant K  | Denominator of $H(s)$             | Numerator of $H(s)$                                                 | ( <b>dB</b> ) |

| 2 | 0.38540     | $s^2 + 3.92705$                   | $s^2 + 1.03153s + 1.60319$                                          | 8.3           |

| 3 | 0.31410     | $s^2 + 2.80601$                   | $(s^2 + 0.45286s + 1.14917)(s + 0.766952)$                          | <b>21.9</b>   |

| 4 | 0.015397    | $(s^2 + 2.53555)(s^2 + 12.09931)$ | $(s^2 + 0.25496s + 1.06044)(s^2 + 0.92001s + 0.47183)$              | 36.3          |

| 5 | 0.019197    | $(s^2 + 2.42551)(s^2 + 5.43764)$  | $(s^2 + 0.16346s + 1.03189)(s^2 + 0.57023s + 0.57601)(s + 0.42597)$ | 50.6          |

| 369 - 2.0 | $\Omega_S$ | = | <b>2.0</b> |  |

|-----------|------------|---|------------|--|

|-----------|------------|---|------------|--|

| n            | Constant K  | Denominator of $H(s)$             | Numerator of $H(s)$                                                  | ( <b>dB</b> )    |

|--------------|-------------|-----------------------------------|----------------------------------------------------------------------|------------------|

| 2            | 0.38540     | $s^2 + 3.92705$                   | $s^2 + 1.03153s + 1.60319$                                           | 8.3              |

| 3            | 0.31410     | $s^2 + 2.80601$                   | $(s^2 + 0.45286s + 1.14917)(s + 0.766952)$                           | 21.9             |

| 4            | 0.015397    | $(s^2 + 2.53555)(s^2 + 12.09931)$ | $(s^2 + 0.25496s + 1.06044)(s^2 + 0.92001s + 0.47183)$               | 36.3             |

| _5           | 0.019197    | $(s^2 + 2.42551)(s^2 + 5.43764)$  | $(s^2 + 0.16346s + 1.03189)(s^2 + 0.57023s + 0.57601)(s + 0.42597)$  | 50.6             |

| Ω            | g = 2.0     |                                   |                                                                      |                  |

|              | Denominator |                                   |                                                                      | Amin             |

| n            | Constant K  | Denominator of $H(s)$             | Numerator of $H(s)$                                                  | ( <b>dB</b> )    |

| 2            | 0.20133     | $s^2 + 7.4641$                    | $s^2 + 1.24504s + 1.59179$                                           | 13. <b>9</b>     |

| 3            | 0.15424     | $s^2 + 5.15321$                   | $(s^2 + 0.53787s + 1.14849)(s + 0.69212)$                            | 31.2             |

| 4            | 0.0036987   | $(s^2 + 4.59326)(s^2 + 24.22720)$ | $(s^2 + 0.30116s + 1.06258)(s^2 + 0.88456s + 0.41032)$               | 48.6             |

| 5            | 0.0046205   | $(s^2 + 4.36495)(s^2 + 10.56773)$ | $(s^2 + 0.19255s + 1.03402)(s^2 + 0.58054s + 0.52500)(s + 0.392612)$ | <b>66</b> .1     |

| $\Omega_{s}$ | s = 3.0     |                                   |                                                                      |                  |

|              | Denominator |                                   |                                                                      | A <sub>min</sub> |

| n            | Constant K  | Denominator of $H(s)$             | Numerator of $H(s)$                                                  | ( <b>dB</b> )    |

| 2            | 0.083974    | $s^2 + 17.48528$                  | $s^2 + 1.35715s + 1.55532$                                           | 21.5             |

| 3            | 0.063211    | $s^2 + 11.82781$                  | $(s^2 + 0.58942s + 1.14559)(s + 0.65263)$                            | 42.8             |

| $\Omega_S$ | = | 3.0 |

|------------|---|-----|

|            |   |     |

|   | Denominator |                                 |                                                                     | A <sub>min</sub> |

|---|-------------|---------------------------------|---------------------------------------------------------------------|------------------|

| n | Constant K  | Denominator of $H(s)$           | Numerator of $H(s)$                                                 | ( <b>dB</b> )    |

| 2 | 0.083974    | $s^2 + 17.48528$                | $s^2 + 1.35715s + 1.55532$                                          | 21.5             |

| 3 | 0.063211    | $s^2 + 11.82781$                | $(s^2 + 0.58942s + 1.14559)(s + 0.65263)$                           | 42.8             |

| 4 | 0.00062046  | $(s^2 + 10.4554)(s^2 + 58.471)$ | $(s^2 + 0.32979s + 1.063281)(s^2 + 0.86258s + 0.37787)$             | 64.1             |

| 5 | 0.00077547  | $(s^2 + 9.8955)(s^2 + 25.0769)$ | $(s^2 + 0.21066s + 1.0351)(s^2 + 0.58441s + 0.496388)(s + 0.37452)$ | 85.5             |

and  $C_n(\Omega)$  is calculated using

$$C_n(\Omega) = 2\Omega C_{n-1}(\Omega) - C_{n-2}(\Omega) \tag{2.16}$$

where

$$C_1(\Omega) = \Omega \tag{2.17}$$

$$C_0(\Omega) = 1 \tag{2.18}$$

The normalised loss transfer function  $H_L(s)$  is given by [21]

$$H_L(s) = \prod_j \frac{1}{K} (s - s_j)$$

(2.19)

with

$$s_j$$

is the left-hand plane roots of

$$1 + \varepsilon^2 C_n^2 \left(\frac{s}{j}\right) = 0 \tag{2.20}$$

and is denormalised by replacing

s with

$$\frac{s}{\omega_P}$$

(2.21)

K is adjusted in order to provide 0 dB loss at the passband minima [21].

When a low-pass filter is designed using the Chebyshev approximation and the specification given in Table 2.1, the filter is a 3rd order filter with the following transfer function:

$$H_F(s) = \frac{1.7753 \times 10^{11}}{(s^3 + 7.8723 \times 10^3 s^2 + 6.0595 \times 10^7 s} + 1.7753 \times 10^{11})$$

(2.22)

### 2.5.1.3 Butterworth

The Butterworth approximation has the characteristic that its slope is close to zero at DC [21]. The amplitude of the transfer function is then optimally flat throughout the passband, as seen in

Figure 2.9(b). The Butterworth approximation is therefore used where the magnitude of the signal throughout the passband must be preserved in the frequency domain.

All the transfer functions discussed so far, including the Butterworth approximation, do not have a linear phase response and therefore causes the output to ring when a step input is applied to the filter, as seen in Figure 2.9(a).

The loss transfer function for the Butterworth approximation is described by [21]

$$|H_L(j\omega)| = \left|\frac{V_{in}(j\omega)}{V_{out}(j\omega)}\right| = \sqrt{1 + \varepsilon^2 \left(\frac{\omega}{\omega_P}\right)^{2n}}$$

(2.23)

where  $\varepsilon$  a constant given by

$$\varepsilon = \sqrt{10^{0.1A_{max}} - 1} \tag{2.24}$$

and the order n calculated with

$$n = \frac{\log_{10} \left(\frac{10^{0.1A_{min}} - 1}{\varepsilon^2}\right)}{\log_{10} \left(\frac{\omega_S}{\omega_P}\right)^2}$$

(2.25)

The normalised loss transfer function  $H_L(s)$  is described by [21]

$$H_L(s) = \prod_j (s - s_j) \tag{2.26}$$

with  $s_j$  the left half plane roots of

$$1 + (-s^2)^n = 0 (2.27)$$

and is denormalised by replacing

s with

$$s\left(\frac{\varepsilon^{1/n}}{\omega_P}\right)$$

(2.28)

The gain transfer function  $H_F(s)$  is then given by

$$H_F(s) = \frac{V_{out}(s)}{V_{in}(s)} = \frac{1}{H_L(s)}$$

(2.29)

When a low-pass filter is designed using the Butterworth approximation and the specification given

in Table 2.1, the filter is a 4th order filter with the following transfer function:

$$H_F(s) = \frac{4.4618 \times 10^{15}}{(s^4 + 2.1357 \times 10^4 \ s^3 + 2.2806 \times 10^8 \ s^2 + 1.4266 \times 10^{12} \ s + 4.4618 \times 10^{15})}$$

(2.30)

### 2.5.1.4 Bessel

The Bessel approximation is used to approximate a loss transfer function that has a delay characteristic which is optimally flat throughout the passband. This results in a loss transfer function which has a linear phase characteristic throughout the passband. The Bessel approximation is therefore used where the phase of signal components must be preserved [21].

As seen in Figure 2.9(a), the filter has the best step response of all the approximations, but at a cost. The magnitude of the frequency response shows a very slow transition from the passband to the stopband and therefore the transfer function order is the highest of all the approximations.

The higher order allows the knee frequency of the Bessel approximation to be much higher than the other approximations, resulting in the shortest group delay of all the approximations. If, however, the group delay is compared to the group delay of the same order transfer functions designed with the other approximations, using the same knee frequency, the Bessel approximation will have the longest group delay of all.

The normalised loss transfer function for the Bessel approximation is given by [21]

$$H_L(s) = \frac{V_{in}(s)}{V_{out}(s)} = \frac{B_n(s)}{B_n(0)}$$

(2.31)

with  $B_n(s)$  calculated using the following recursive formula:

$$B_n(s) = (2n-1)B_{n-1}(s) + s^2 B_{n-2}(s)$$

(2.32)

where

$$B_1(s) = s + 1 (2.33)$$

$$B_0(s) = 1 (2.34)$$

28

The transfer function is denormalised by replacing [21]

$$s \text{ with } sT_0$$

(2.35)

where

$$T_0 = \frac{\Omega}{\omega} \tag{2.36}$$

with  $\Omega$  the normalised frequency and  $\omega$  the denormalised frequency.

The gain transfer function  $H_F(s)$  is then given by

$$H_F(s) = \frac{V_{out}(s)}{V_{in}(s)} = \frac{1}{H_L(s)}$$

(2.37)

When a low-pass filter is designed using the Bessel approximation and the specification given in Table 2.1, the filter is a 6th order filter with the following transfer function:

$$H_F(s) = \frac{3.2404 \times 10^{26}}{(s^6 + 1.1781 \times 10^5 \ s^5 + 6.6091 \times 10^9 \ s^4} + 2.2246 \times 10^{14} s^3 + 4.6800 \times 10^{18} s^2 + 5.7761 \times 10^{22} s + 3.2404 \times 10^{26})$$

(2.38)

### 2.5.2 Impact on AMB performance

According to [22] the addition of filters within the control loop of the AMB has the effect of increasing the natural frequency  $(\omega_n)$  of the closed-loop system. This has the effect of increasing the second order equivalent stiffness  $(k_{eq})$  of the system, while the increase in  $(b_{eq})$  is less prominent. The static stiffness of the AMB remains unchanged as it is dependent on the DC characteristics of the AMB. Interface filters also have the effect of reducing the dynamic stiffness of the AMB at high frequencies.

# 2.6 Conclusion

There are various issues which have to be addressed when designing a digital AMB controller, some of which are interfacing, algorithm implementation and sampling rate.

The interfacing consists of two components, namely the AAF and AIF. The AAF is used to bandwidth limit the input to the controller in order to prevent aliasing, while the AIF is used to bandwidth limit the controller's output in order to prevent imaging. As AMB systems generally have a low-pass transfer characteristic, an AIF is usually unnecessary.

The PID control law is transformed into a discrete second order transfer function and can then be implemented using the 3D direct filter structure as discussed. The 3D filter structure aids coefficient insensitivity and is computationally efficient.

The controller's sampling rate is of utmost importance as it determines the controller's bandwidth. It also determines the frequency content of the controller's input and therefore influences the AAF design.

When selecting a filter approximation, it is important to consider the phase characteristic of the approximations, as the controller is highly dependent on the amplitude and phase of the input signal.

# **Chapter 3**

# System Design

This chapter discusses the design and specification of the embedded AMB controller. It starts off with the design process, which is followed by the detail system design and is concluded with detailed simulations of the closed-loop system including interface filters and DSP firmware.

# 3.1 Design process

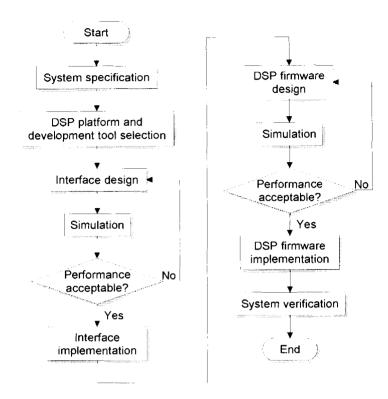

Figure 3.1 illustrates the design process for the development of the embedded AMB controller. As the design process is iterative in nature, only the final iteration is discussed in this chapter. The process is summarised as follows:

- 1. The performance and interface requirements of the controller is specified.

- 2. The appropriate DSP platform and development tools are selected.

- 3. The interface circuitry is designed with the system and DSP interface requirements in mind. The closed-loop system response is then simulated using an analogue PID controller. The interface circuitry is implemented once the performance is acceptable.

Figure 3.1: Controller design process

- 4. The DSP firmware is designed with the controller requirements in mind. The closed-loop system response is simulated including the firmware. The firmware is implemented if the controller meets the specified requirements.

- 5. The overall system performance is verified.

Steps 1 and 2 as well as the design and simulation of steps 3 and 4 are discussed in detail in the following sections. The implementation of steps 3 and 4 is discussed in Chapter 4 and step 5 is discussed in Chapter 5.

# **3.2** System specification

The embedded controller is specified according to the system's control parameters and the system interfaces, namely:

- AMB interface,

- PC interface,

- User interface, and

- Mains interface.

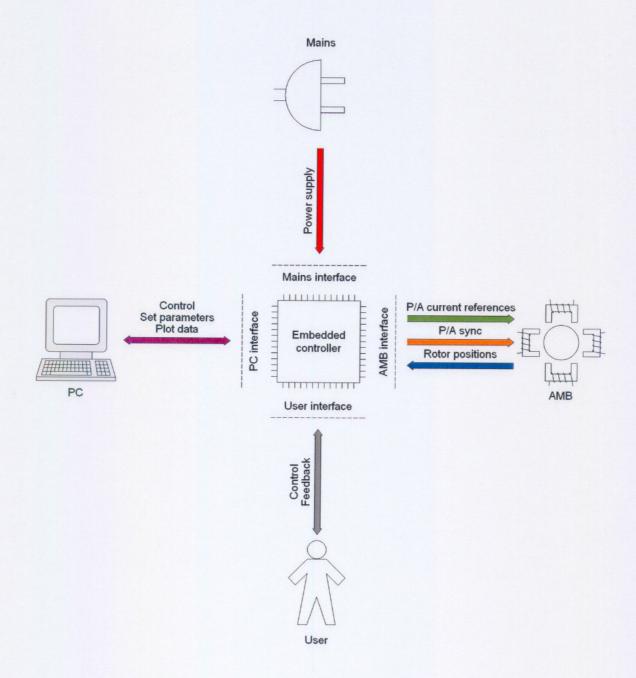

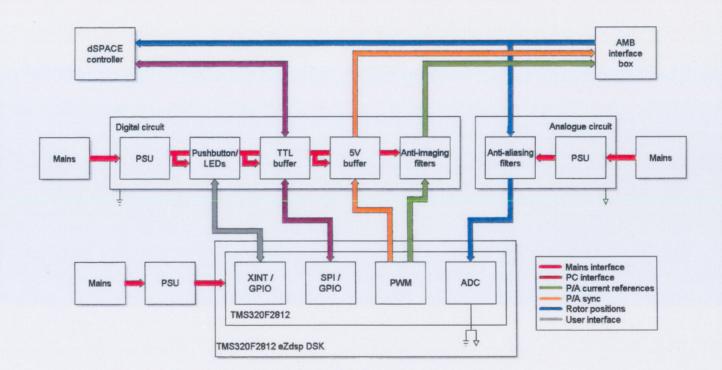

A visual representation of the system interfaces is shown in Figure 3.2. Each aspect of the system specification will now be discussed in detail. A summary of the system specification is given at the end of the section in Table 3.1.

**Control parameters:** The embedded controller is intended to fully suspend and actively control an active magnetic bearing system with rotor speeds of up to 30 000 rpm. It will be used to suspend an existing double radial AMB model, which requires four axes to be controlled with a PID control law. There should, however, be adequate processing speed to control a fully suspended AMB system with five axes.

**Closed-loop system performance:** The static stiffness and equivalent second order stiffness of the embedded controller shall be compared with the existing  $dSPACE^{\textcircled{B}}$  controller. A maximum deviation of 20 % will be tolerated.

**AMB interface:** The AMB interface consists of three types of signals, namely the current reference output, the power amplifier synchronisation output and the rotor position input. The nature of these signals are determined by the interface of the existing double radial AMB model. The controller must therefore have the following interface signals [10]:

#### 3.2. SYSTEM SPECIFICATION

Figure 3.2: System interfaces

- Two current reference outputs for each axis with a range of *approximately* 2.5 to 10 V, representing a current range of 0 to 10 A.

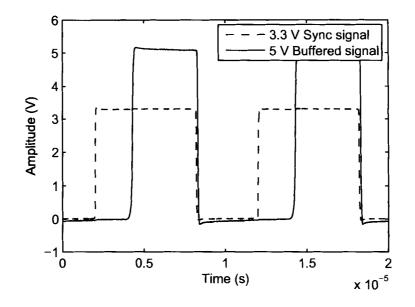

- A single square wave with a voltage range of 0 to 5 V, a frequency of 100 kHz and a variable pulse width is used to synchronise the power amplifiers.

- One rotor position input per axis, having a sensitivity of 7.87 mV/ $\mu$ m with a DC offset, resulting in a range of *approximately* 0 to -10 V for 600 to -600  $\mu$ m.

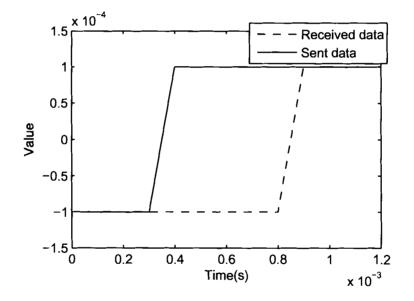

**PC interface:** The PC interface enables real-time performance analysis and control of the AMB through a high-speed digital communications link. In order to perform performance analysis, the user must be capable of setting the position reference for a given axis for every control cycle and be able to plot the rotor position using a graphical interface. The user must also be able to update the PID constants and turn the AMB on and off using the graphical interface. The embedded controller should be able to operate in a stand-alone mode and can therefore not be dependent on the PC interface for normal operation.