# An integrated controller for an active magnetic bearing system

A dissertation presented to

The School of Electrical Electronic and Computer Engineering

North-West University

In partial fulfilment of the requirements of the degree

Master Ingeneriae

in Electronic and Computer Engineering

by

#### Jacques Jansen van Rensburg

Supervisor: Prof. G. van Schoor Assistant supervisor: Mr. A.C. Niemann

December 2007

Potchefstroom Campus

# DECLARATION

I hereby declare that all the material incorporated in this thesis is my own original unaided work except where specific reference is made by name or in the form of a numbered reference. The word herein has not been submitted for a degree at another university.

Signed:

\_\_\_\_\_

Jacques Jansen van Rensburg

. . ......

#### SUMMARY

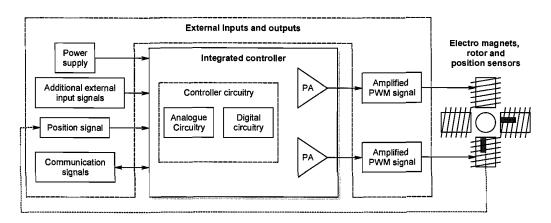

An active magnetic bearing (AMB) involves the suspension of a rotor by means of electromagnetic actuators. An AMB system comprises actuators, position sensors, a controller and power amplifiers. Conventional position sensors for rotor position sensing are expensive. The McTronX Research Group at the North-West University is currently conducting research on self-sensing, a method of extracting rotor position from the current and voltage actuation signals of the AMB.

It was deemed necessary to develop a complete platform that will enable the implementation of self-sensing algorithms. The platform incorporates analogue circuitry, embedded devices and switching power amplifiers. The system will thus integrate all the electronics required for AMB suspension, and is thus dubbed: an Integrated Controller.

The development of the integrated controller presented unique design challenges not yet faced by the McTronX group. To increase the chances of success and minimize some of the risks, the integrated controller was developed in collaboration with an industry partner.

The collaboration required a systems engineering approach to the project. A detail type B specification was drawn up to aid in the project management process. The specification includes important detail such as the functional architectures, functional capabilities, performance specifications and physical constraints of the integrated controller.

Some self-sensing algorithms can be implemented by means of analogue circuitry, and some can only be implemented in the digital domain. These digital algorithms are computationally intensive and require powerful processors. Digital signal processors (DSPs) and field programmable gate arrays (FPGAs) both exhibit unique architectures ideal for digital signal processing. Both these devices were implemented in the integrated controller, with the DSP as the main processor and the FPGA the co-processor.

Although the integrated controller can operate as a stand-alone system, it has several communication interfaces (RS485, USB and RS232). This allows the system to work in conjunction with other integrated controllers, to be controlled by a master controller or to communicate to a personal computer (PC).

Testing the integrated controller involved the closed loop current control of an AMB power amplifier, facilitating all critical functional aspects. The integrated controller's performance meets the required specifications and is expected to successfully facilitate future self-sensing investigations.

. . ..

#### **OPSOMMING**

'n Aktiewe magnetiese laer (AML) behels die suspendering van 'n rotor deur middel van elektromagnetiese aktueerders. 'n AML stelsel bestaan tipies uit aktueerders, posisiesensors, 'n beheerder en kragversterkers. Die konvensionele sensors wat gebruik word om rotorposisie te bepaal is baie duur. Die McTronX navorsingsgroep by die Noordwes Universiteit is tans besig om self-waarneming na te vors, 'n metode om die rotorposisie af te lei vanaf die spanning en stroom aktueerseine van die AML.

'n Behoefte vir 'n platform waarop self-waarneming algoritmes geïmplementeer kan word, het ontstaan. Die platform integreer analoogelektronika, ingebedde beheerders en skakelmodus kragversterkers wat al die benodige komponente uitmaak van 'n AML beheerstelsel. Die platform is dan sodanig 'n geïntegreerde beheerder gedoop.

Die ontwikkeling van die geïntegreerde beheerder het 'n paar unieke uitdagings aan die McTronX groep gestel, sommige waarmee die groep nog nie te doen gehad het nie. Om die suksesvolle afhandeling van die projek te verseker, is 'n paar van die risiko's verminder deur die geïntegreerde beheer te ontwikkel in samewerking met 'n industriële vennoot.

Die projek is benader uit 'n stelsel ingenieurs oogpunt wat onder andere die opstelling van 'n tipe B spesifikasie behels het. Die spesifikasie sluit onder andere detail in soos funksionele argitekture, operasionele funksies, werkverrigting spesifikasies en fisiese beperkinge van die geïntegreerde beheerder.

Sommige self-waarnemings algoritmes kan met behulp van analoogelektronika uitgevoer word en ander slegs met die hulp van digitale beheerders. Die digitale algoritmes benodig kragtige prosesserings vermoë wat deur 'n digitale seinverwerker (DSP) en/of 'n *field programmable gate array* (FPGA) bevredig kan word. Altwee die toestelle is op die geïntegreerde beheerder geïmplementeer; die DSP as die hoofverwerker en FPGA as die hulpverwerker.

Alhoewel die geïntegreerde beheerder kan funksioneer as 'n alleenstaande stelsel, beskik dit oor verskeie kommunikasie-intervlakke (RS485, RS232, USB). Dit stel die stelsel in staat om te kommunikeer met ander geïntegreerde beheerders, om beheer te word deur 'n meesterbeheerder of om te kommunikeer met 'n persoonlike rekenaar (PC).

Die evaluering van die geïntegreerde beheerder het behels die sluiting van 'n AML kragversterker stroom lus. Al die kritiese aspekte van die geïntegreerde beheerder is deur hierdie metode geëvalueer. Daar word verwag dat die geïntegreerde beheerder voldoende sal wees vir self-waarneming ondersoeke aangesien dit aan die basiese spesifikaies voldoen.

### ACKNOWLEDGEMENTS

A special thanks to M-Tech Industrial and THRIP for funding this research and granting me the opportunity to further my studies.

I would also like thank the following people who's contributions were invaluable during the course of this project.

- Professor George van Schoor, my supervisor, for his guidance, advice and for laying the foundations for the success of this project.

- André Niemann, my assistant supervisor, for his dedication, guidance and advice.

- Rob Hudson, who provided technical expertise, support and hours spent on design central to the success of this project.

- My family, for their unwavering love and support.

-----

# Contents

| Summer               | <b>y</b> |                                                   | i  |

|----------------------|----------|---------------------------------------------------|----|

| Opsomm               | ning     |                                                   | ii |

| Acknow               | ledgen   | nents i                                           | ii |

| List of fig          | gures    | xi                                                | ii |

| List of ta           | bles     | x                                                 | v  |

| List of at           | brevi    | ations x                                          | vi |

| List of symbols xvii |          |                                                   | ii |

| 1 Intro              | ductio   | n                                                 | 1  |

| 1.1                  | Backgı   | round                                             | 1  |

|                      | 1.1.1    | Basic active magnetic bearing operating principle | 1  |

|                      | 1.1.2    | Digital Controller                                | 2  |

|                      | 1.1.3    | System architecture                               | 3  |

| 1.2                  | Proble   | m statement                                       | 4  |

| 1.3                  | Issues   | to be addressed and methodology                   | 5  |

|                      | 1.3.1    | Conceptual analysis                               | 5  |

|   |      | 1.3.2    | System specification                                     | 7  |

|---|------|----------|----------------------------------------------------------|----|

|   |      | 1.3.3    | Sub-system procurement                                   | 7  |

|   |      | 1.3.4    | System integration                                       | 7  |

|   |      | 1.3.5    | System evaluation                                        | 8  |

|   | 1.4  | Docur    | nent overview                                            | 8  |

|   |      | 1.4.1    | Chapter 2: Literature study                              | 8  |

|   |      | 1.4.2    | Chapter 3: System specification                          | 8  |

|   |      | 1.4.3    | Chapter 4: Sub-system design and evaluation              | 8  |

|   |      | 1.4.4    | Chapter 5: Integrated controller hardware and evaluation | 9  |

|   |      | 1.4.5    | Chapter 6: Conclusions and recommendations               | 9  |

| 2 | Lite | rature s | study                                                    | 10 |

|   |      |          | •                                                        |    |

|   | 2.1  | Self-se  | ensing                                                   | 10 |

|   |      | 2.1.1    | Basic magnetic bearing model                             | 11 |

|   |      | 2.1.2    | Amplitude modulation approach                            | 13 |

|   | 2.2  | Proces   | ssors                                                    | 17 |

|   |      | 2.2.1    | Digital signal processors (DSP)                          | 18 |

|   |      | 2.2.2    | Field programmable gate array (FPGA)                     | 21 |

|   |      | 2.2.3    | Co-processing                                            | 24 |

|   | 2.3  | Comm     | nunication                                               | 25 |

|   |      | 2.3.1    | CAN bus                                                  | 25 |

|   |      | 2.3.2    | RS232                                                    | 26 |

|   |      | 2.3.3    | RS485                                                    | 27 |

|   | 2.4  | System   | ms Engineering                                           | 29 |

|   |      | 2.4.1    | System life-cycle                                        | 31 |

|   |      | 2.4.2    | System specification                                     | 31 |

"I can do everything through Him who gives me strength." Philippians 4:13

|   |             | 2.4.3   | Conclusion                                      | 33 |

|---|-------------|---------|-------------------------------------------------|----|

| 3 | Syst        | em spe  | cification                                      | 34 |

|   |             | 3.0.4   | Introduction                                    | 34 |

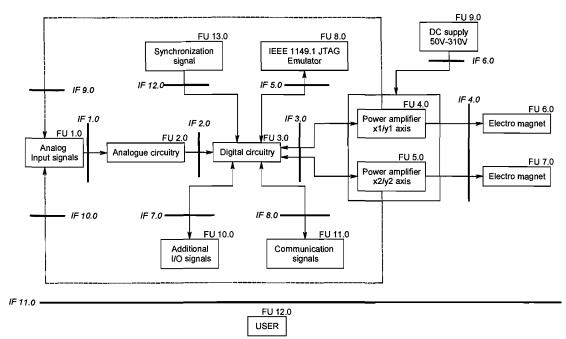

|   | 3.1         | Integr  | ated controller functional architecture         | 35 |

|   |             | 3.1.1   | System functional architecture                  | 35 |

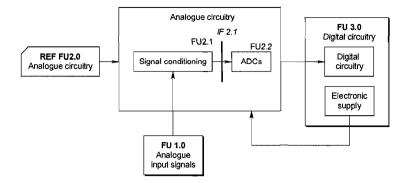

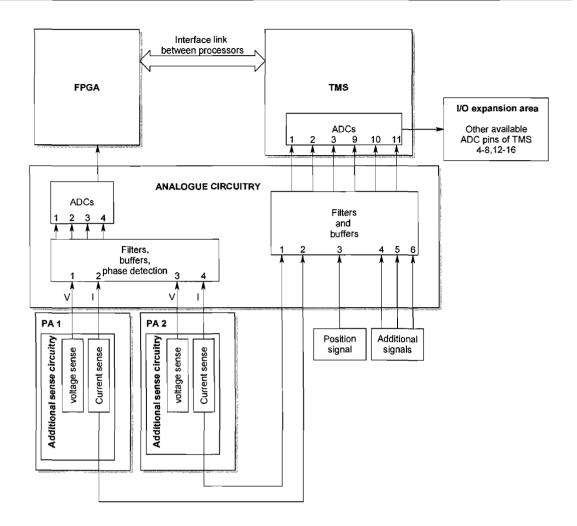

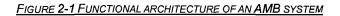

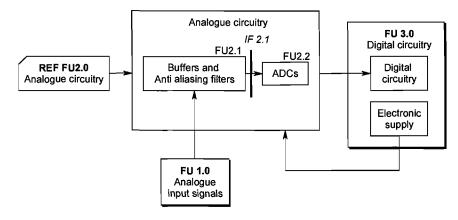

|   |             | 3.1.2   | Analogue circuitry functional architecture      | 37 |

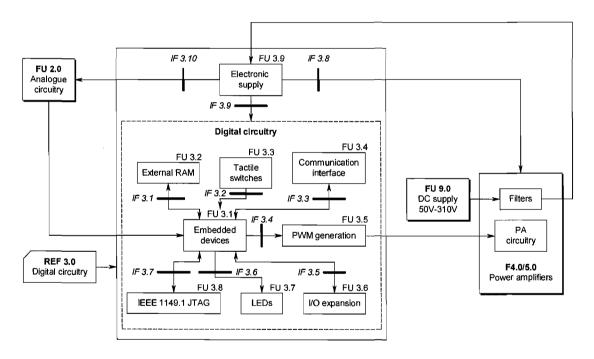

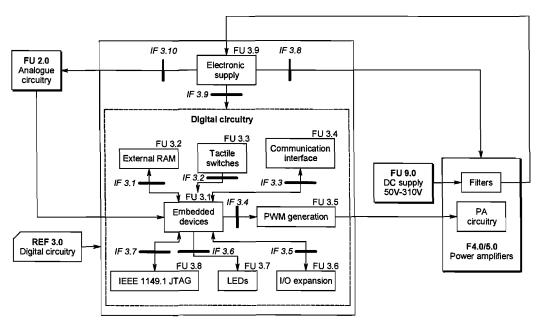

|   |             | 3.1.3   | Digital circuitry functional architecture       | 38 |

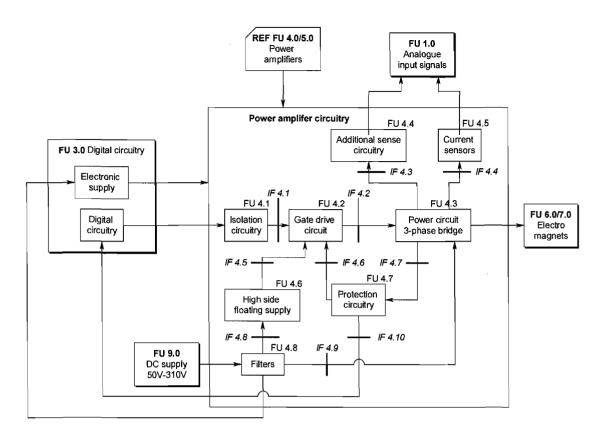

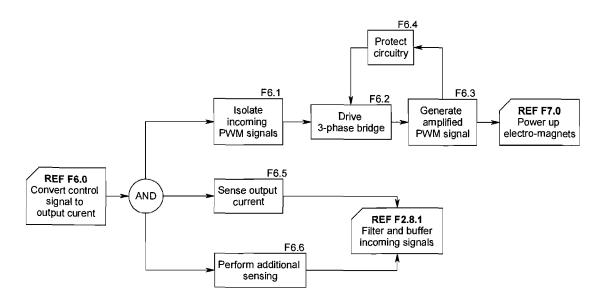

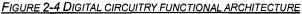

|   |             | 3.1.4   | Power amplifier functional architecture         | 39 |

|   | 3.2         | Subse   | ction functional capability flow                | 41 |

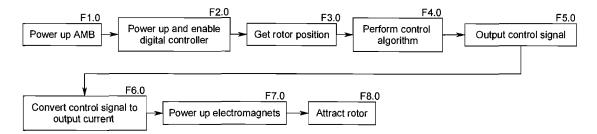

|   |             | 3.2.1   | AMB functional flow                             | 41 |

|   |             | 3.2.2   | Functional capabilities of the controller       | 42 |

|   |             | 3.2.3   | Functional capabilities of the power amplifiers | 44 |

|   |             | 3.2.4   | Allocations                                     | 46 |

|   |             | 3.2.5   | Resource allocation                             | 47 |

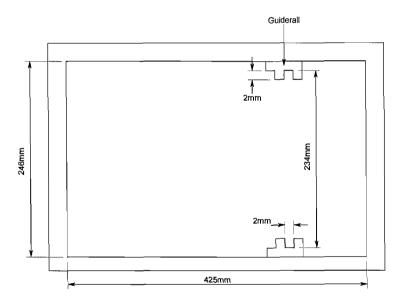

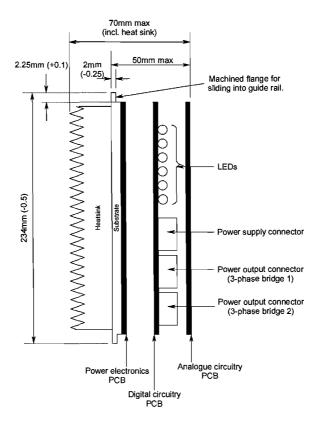

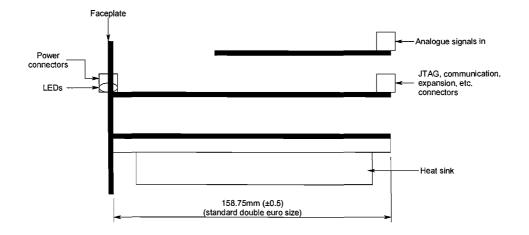

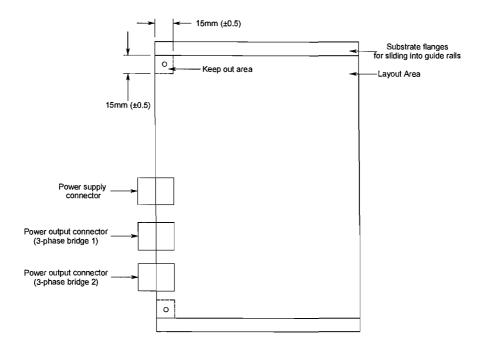

|   | 3.3         | Mecha   | anical requirements                             | 47 |

|   | 3.4         | Concl   | usion                                           | 51 |

| 4 | Sub         | -svster | n design and evaluation                         | 52 |

| - | <b>4</b> .1 | 5       | dded devices                                    | 52 |

|   | 4,1         |         |                                                 |    |

|   |             | 4.1.1   | DSP                                             | 52 |

|   |             | 4.1.2   | Computational complexity                        | 54 |

|   |             | 4.1.3   | FPGA                                            | 57 |

|   | 4.2         | RS485   | 5 design                                        | 59 |

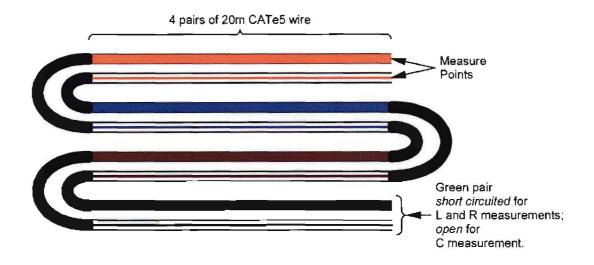

|   |             | 4.2.1   | Characteristic impedance of transmission line   | 60 |

|   |             | 4.2.2   | Termination resistors                           | 61 |

......

-----

· · · · · · · · · · · · ·

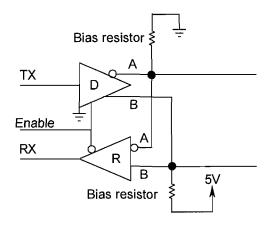

|   |       | 4.2.3  | Bias resistors                             | 62 |

|---|-------|--------|--------------------------------------------|----|

|   |       | 4.2.4  | Implementation                             | 63 |

|   |       | 4.2.5  | Evaluation                                 | 65 |

|   | 4.3   | Conclu | usions                                     | 68 |

|   |       | 4.3.1  | RS485                                      | 68 |

|   |       | 4.3.2  | Computational complexity                   | 68 |

| 5 | Integ | grated | controller hardware and evaluation         | 69 |

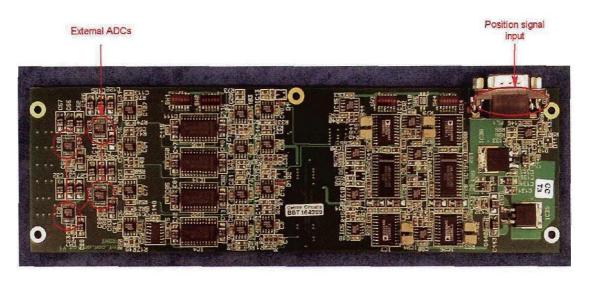

|   | 5.1   | Integr | ated controller hardware                   | 69 |

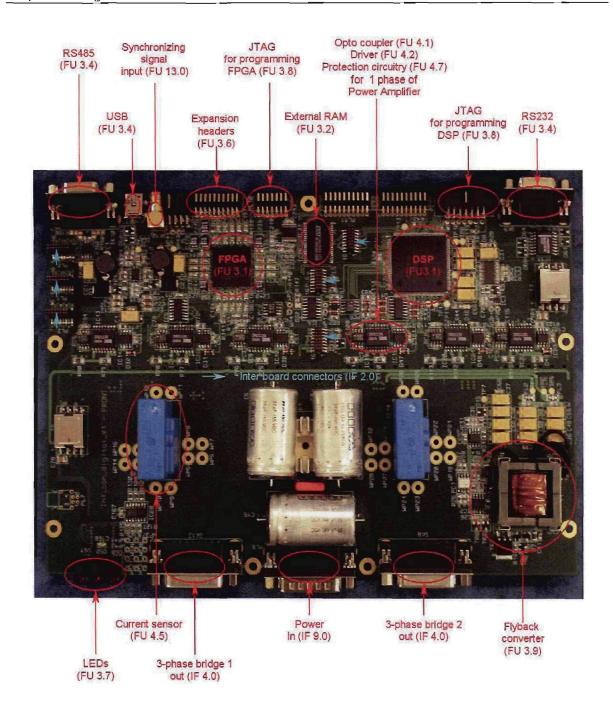

|   |       | 5.1.1  | Analogue PCB                               | 69 |

|   |       | 5.1.2  | Controller PCB                             | 70 |

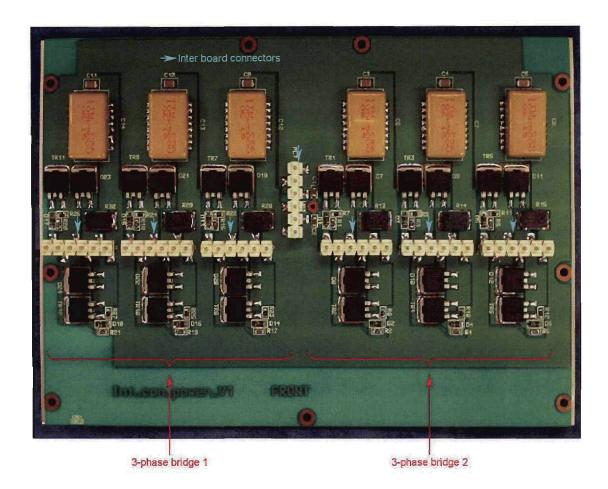

|   |       | 5.1.3  | Power amplifier PCB                        | 70 |

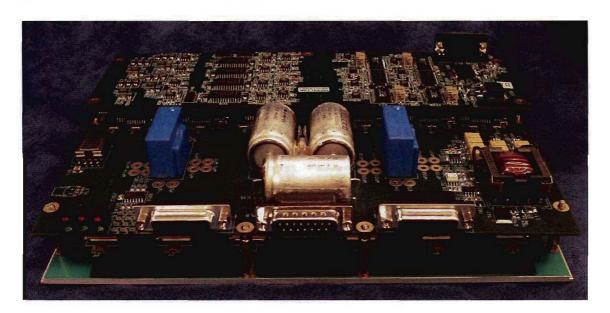

|   |       | 5.1.4  | Integrated system                          | 72 |

|   | 5.2   | Evalu  | ation                                      | 73 |

|   |       | 5.2.1  | Evaluation process                         | 73 |

|   |       | 5.2.2  | Flyback converter outputs                  | 76 |

|   |       | 5.2.3  | Initial evaluation of power amplifier      | 77 |

|   |       | 5.2.4  | Current limiting tests on power amplifiers | 80 |

|   |       | 5.2.5  | ADC inputs                                 | 82 |

|   |       | 5.2.6  | Power amplifier closed loop control        | 82 |

|   |       | 5.2.7  | Algorithm evaluation                       | 86 |

|   |       | 5.2.8  | Conclusion                                 | 90 |

| 6 | Con   | clusio | n and recommendations                      | 91 |

|   | 6.1   | Powe   | r amplifiers                               | 91 |

|   | 6.2   | Algor  | rithms                                     | 92 |

. . . . . . . . . . . . .

······

a server a server server and a server s

------

| Bi | bliog | raphy             | 95 |

|----|-------|-------------------|----|

|    | 6.5   | Conclusion        | 94 |

|    | 6.4   | Future work       | 93 |

|    | 6.3   | Integrated system | 93 |

### Appendices

...

. .....

97

------

.....

------

. . . . . .

# **List of Figures**

| 1.1  | Representation of AMB system              | 2  |

|------|-------------------------------------------|----|

| 1.2  | Current AMB control system configuration  | 3  |

| 1.3  | Proposed AMB control system configuration | 4  |

| 2.1  | Types of self sensing                     | 11 |

| 2.2  | AMB self-sensing setup                    | 11 |

| 2.3  | Magnetic circuit                          | 12 |

| 2.4  | Amplitude modulation self sensing         | 14 |

| 2.5  | Actual position of rotor                  | 14 |

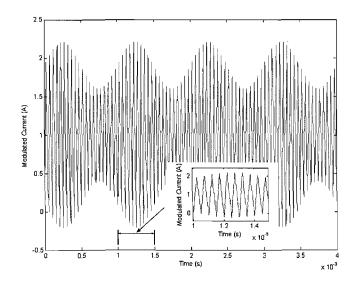

| 2.6  | Modulated current                         | 15 |

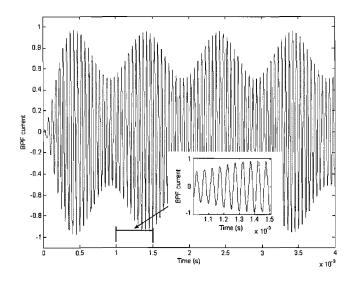

| 2.7  | Current after band pass filter            | 15 |

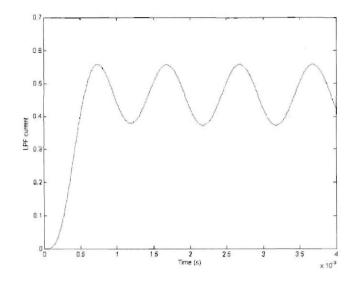

| 2.8  | Current after low passed filter           | 16 |

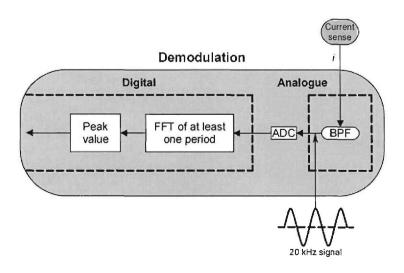

| 2.9  | Demodulation using an FFT                 | 16 |

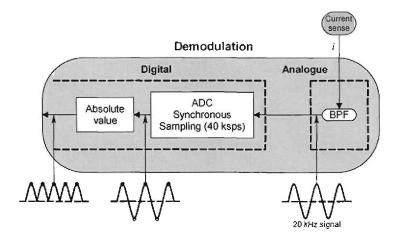

| 2.10 | Demodulation using synchronous sampling   | 17 |

| 2.11 | Illustration of pipelining                | 20 |

| 2.12 | FPGA structure                            | 22 |

| 2.13 | VHDL design flow                          | 23 |

| 2.14 | CAN bus                                   | 25 |

| 2.15 | CAN bus signals                           | 26 |

| 2.16 | RS232 bus                                                            | 27         |

|------|----------------------------------------------------------------------|------------|

| 2.17 | RS485 receiver and signal levels                                     | 28         |

| 2.18 | RS485 transmitter and signal levels                                  | 28         |

| 2.19 | RS485 bus                                                            | 29         |

| 2.20 | Product and system life cycles                                       | 31         |

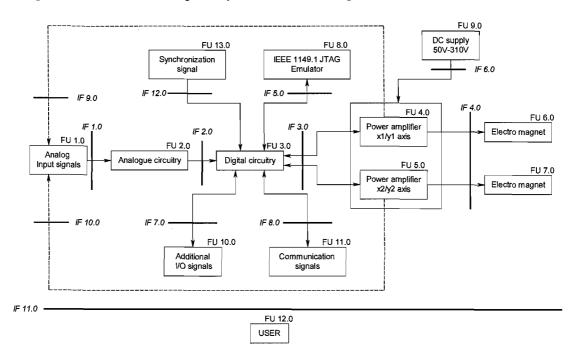

| 3.1  | Functional unit architecture of the integrated controller            | 35         |

| 3.2  | Functional unit architecture of the analogue circuitry               | 38         |

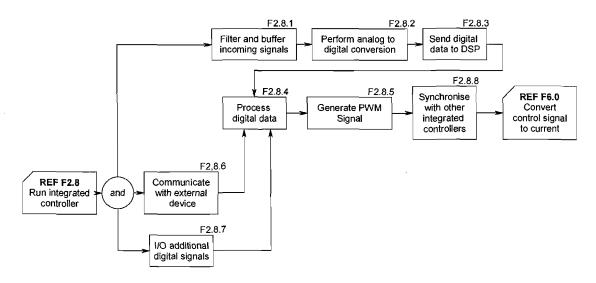

| 3.3  | Functional unit architecture of the digital circuitry                | 38         |

| 3.4  | Functional unit architecture of the power amplifiers                 | 40         |

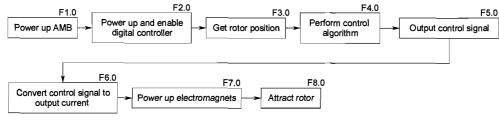

| 3.5  | Functional flow of the AMB system                                    | 41         |

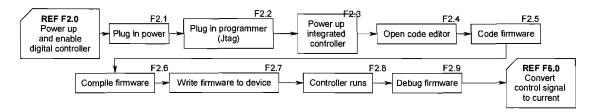

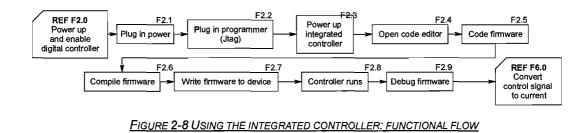

| 3.6  | Using the integrated controller: functional flow                     | <b>4</b> 1 |

| 3.7  | Functions of the integrated controller                               | 42         |

| 3.8  | Analogue input signals                                               | 44         |

| 3.9  | Functions of the power amplifier                                     | 45         |

| 3.10 | Typical 6U Subrack dimensions                                        | 48         |

| 3.11 | Front view of integrated controller                                  | 49         |

| 3.12 | A top view of the integrated controller                              | 50         |

| 3.13 | Side view of integrated controller showing keep out areas            | 50         |

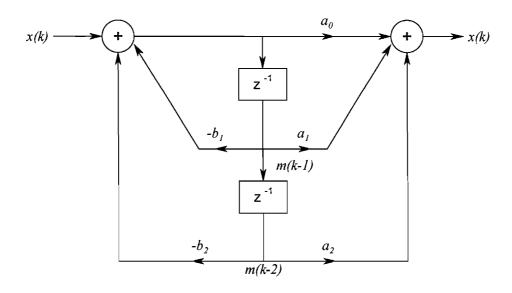

| 4.1  | Second order filter structure                                        | 56         |

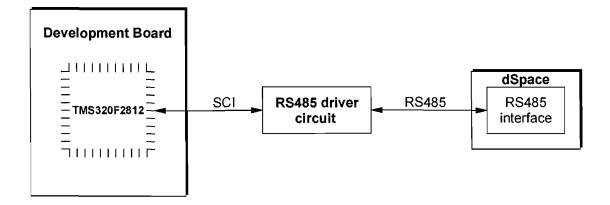

| 4.2  | RS485 configuration for evaluation purposes                          | 60         |

| 4.3  | Series connections between wires in CAT5e cable for RLC measurements | 61         |

| 4.4  | Biased data lines                                                    | 62         |

| 4.5  | RS485 network with bias and terminating resistors                    | 63         |

| 4.6  | RS485 interface circuitry                                            | 64         |

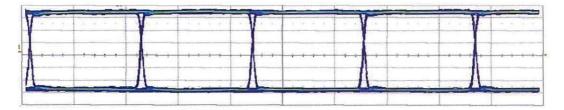

| 4.7  | Baud: 937500 bps, 1 m cable                              | 66 |

|------|----------------------------------------------------------|----|

| 4.8  | Baud: 937500 bps, 1 m cable                              | 67 |

| 4.9  | Baud: 937500 bps, 20 m cable                             | 67 |

| 4.10 | Baud: 292969 bps, 1 m cable                              | 67 |

| 4.11 | Baud: 292969 bps, 20 m cable                             | 68 |

| 5.1  | Analogue PCB                                             | 70 |

| 5.2  | Controller PCB                                           | 71 |

| 5.3  | Power PCB                                                | 72 |

| 5.4  | Integrated controller system                             | 73 |

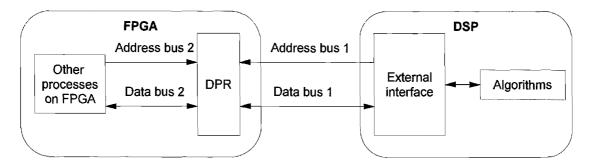

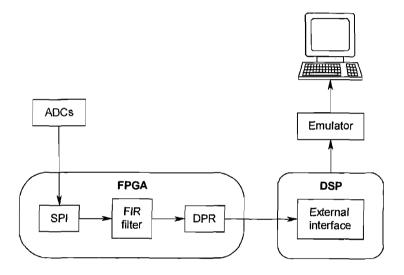

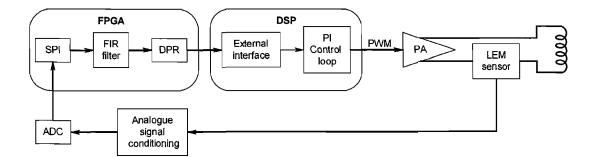

| 5.5  | FPGA and DSP interface via dual port RAM                 | 74 |

| 5.6  | ADC interface evaluation                                 | 76 |

| 5.7  | Power amplifier current control loop                     | 77 |

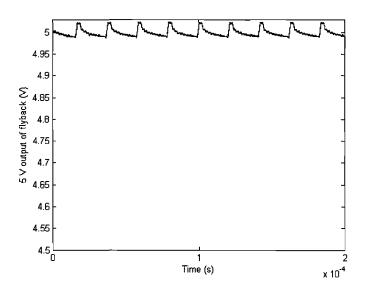

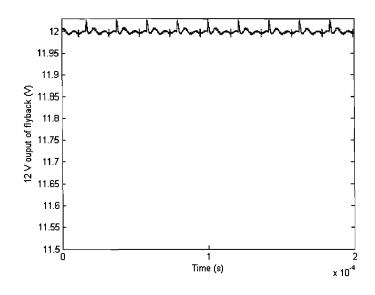

| 5.8  | 5V output voltage of the flyback converter               | 77 |

| 5.9  | 12V output voltage of the flyback converter              | 78 |

| 5.10 | 2-phase configuration                                    | 78 |

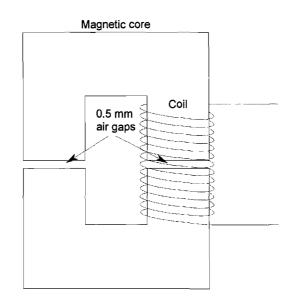

| 5.11 | R-L load with core                                       | 79 |

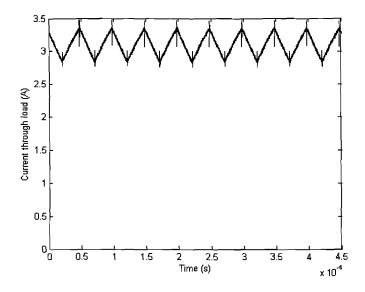

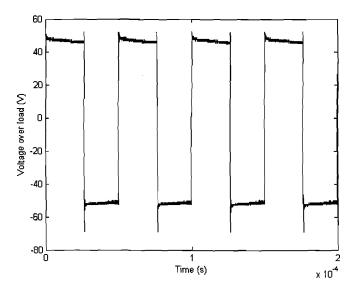

| 5.12 | Ripple current through load                              | 80 |

| 5.13 | PWM voltage across load                                  | 80 |

| 5.14 | Voltage on shutdown pin and current through load         | 81 |

| 5.15 | Current spikes                                           | 82 |

| 5.16 | Voltage at ADC input pin and actual current through load | 83 |

| 5.17 | Power amplifier model                                    | 83 |

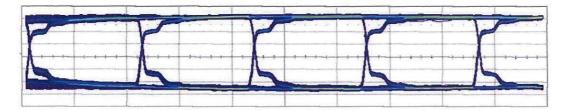

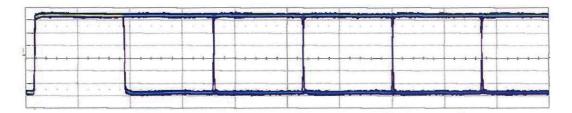

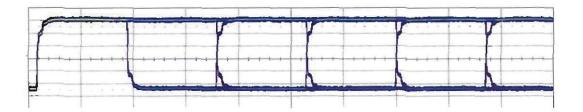

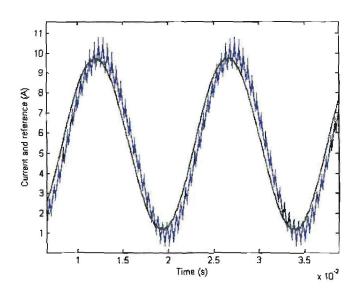

| 5.18 | 680Hz sinusoidal reference                               | 85 |

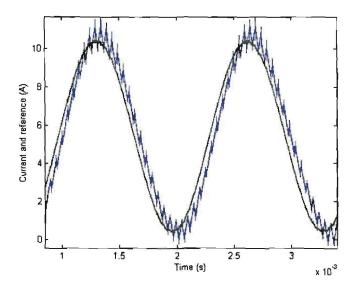

| 5.19 | 760Hz sinusoidal reference                               | 85 |

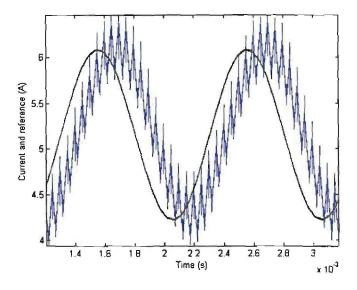

| 5.20 | 1000Hz sinusoidal reference                              | 86 |

xii

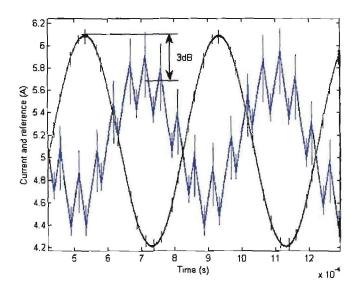

| 5.21 | 2500Hz sinusoidal reference                               | 86 |

|------|-----------------------------------------------------------|----|

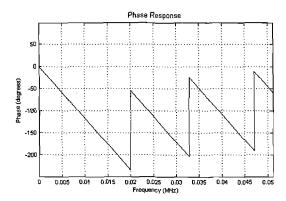

| 5.22 | Magnitude and phase plot of FIR filter implemented in DSP | 87 |

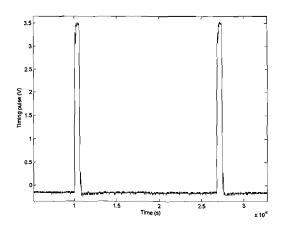

| 5.23 | Execution time of FIR filter on DSP                       | 87 |

| 5.24 | Execution time of PID control on DSP                      | 88 |

| 5.25 | Magnitude plot of FIR filter implemented in FPGA          | 88 |

| 5.26 | Phase plot of FIR filter implemented in FPGA              | 89 |

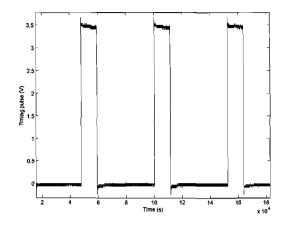

| 5.27 | Execution time of FIR filter on FPGA                      | 89 |

| 5.28 | Execution time of FFT on FPGA                             | 90 |

----

-----

# List of Tables

| 2.1 | CAN bus specifications                                     | 26 |

|-----|------------------------------------------------------------|----|

| 2.2 | RS232 specifications                                       | 27 |

| 2.3 | RS485 specifications                                       | 29 |

| 3.1 | Analogue input signals to integrated controller            | 36 |

| 3.2 | ADCs allocation and requirements                           | 43 |

| 3.3 | Function link table                                        | 46 |

| 3.4 | Work allocation table                                      | 47 |

| 4.1 | Cycles required for a $100^{th}$ order FIR filter $\ldots$ | 54 |

| 4.2 | Number of multiplications and additions for DFT and FFT    | 55 |

| 4.3 | Cycles required for a $4^{th}$ order nonlinear function    | 55 |

| 4.4 | Total cycles required for a self-sensing algorithm         | 57 |

| 4.5 | Attributes of Spartan-3E FPGA                              | 58 |

| 4.6 | Resources required if FFT is implemented on an FPGA        | 59 |

| 4.7 | Summery of data loss results                               | 66 |

| 4.8 | Rise times and unit interval lengths of waveforms          | 67 |

| 5.1 | Peak current spikes for short circuit test                 | 81 |

| 5.2 | FIR specifications                                         | 87 |

| 5.3 | Resources consumed by FIR filter                           | 88 |

\_\_\_\_\_\_

| 5.4 | Resources consumed by FFT                                  | 90 |

|-----|------------------------------------------------------------|----|

| 6.1 | Resources consumed on FPGA according to evaluation results | 92 |

| 6.2 | Resources consumed on DSP according to evaluation results  | 92 |

### LIST OF ABBREVIATIONS

| ABS    | Absolute value                             |

|--------|--------------------------------------------|

| ADC    | Analogue to digital converter              |

| AMB    | Active magnetic bearing                    |

| ASIC   | Application specific integrated circuit    |

| BPF    | Band pass filter                           |

| CAN    | Controller area network                    |

| CCS    | Code composer studio™                      |

| CLB    | Configurable logic block                   |

| CMOS   | Complementary metal-oxide semiconductor    |

| CPLD   | Configurable logic devices                 |

| CPU    | Central processing unit                    |

| DAC    | Digital to analogue converter              |

| DPR    | Dual port RAM                              |

| DSP    | Digital signal processor/processing        |

| EMIF   | External memory interface                  |

| F x.x  | Function number x.x                        |

| FFT    | Fast fourier transform                     |

| FIR    | Finite impulse response                    |

| FPGA   | Field programmable gate array              |

| FU x.x | Functional unit number x.x                 |

| GPP    | General purpose processor                  |

| HSTL   | High speed transistor logic                |

| I/O    | Input/Output                               |

| IDE    | Integrated development environment         |

| IGBT   | Insulated gate bipolar transistor          |

| ISE    | Integrated software environment            |

| JTAG   | Joint test action group                    |

| kbps   | Kilo bits per second                       |

| LPF    | Low pass filter                            |

| LVDS   | Low voltage differential signalling        |

| LVPECL | Low-voltage positive emitter-coupled logic |

| LVTTL  | Low-voltage transistor-transistor logic    |

| MAC    | Multiply and accumulate                    |

| Mbps   | Mega bits per second                       |

| McBSP  | Multichannel buffered serial port          |

| MIPS   | Million instructions per second            |

| Msps   | Million samples per second                 |

| PA     | Power amplifier                            |

|        |                                            |

------

We have a company of the

----

-----

| РСВ         | Printed circuit board                              |

|-------------|----------------------------------------------------|

| PCI         | Peripheral component interconnect                  |

| PID control | Proportional plus integral plus derivative control |

| PWM         | Pulse width modulation                             |

| RAM         | Random access memory                               |

| ROM         | read only memory                                   |

| RSDS        | Reduced swing differential signalling              |

| RTL         | Register transfer level                            |

| SBC         | Single board computer                              |

| SCI         | Serial communication interface                     |

| SPI         | Serial peripheral interface                        |

| SSTL        | Stub series terminated logic                       |

| TI          | Texas instruments                                  |

| UART        | Universal asynchronous receiver-transmitter        |

| USB         | Universal serial bus                               |

| VHDL        | VHSIC hardware descriptive language                |

| VHSIC       | Very high speed integrated circuits                |

| VLIW        | Very long instruction word                         |

### LIST OF SYMBOLS

| $A, A_g$        | Cross sectional area of stator and air gap respectively                   |

|-----------------|---------------------------------------------------------------------------|

| С               | Capacitance                                                               |

| 8               | Air gap length                                                            |

| i               | Current through coil                                                      |

| I(s)            | Load current                                                              |

| $K_P, K_I, K_D$ | Proportional, Integral and Derivative gain of PID controller respectively |

| L               | Coil inductance                                                           |

| l <sub>c</sub>  | Magnetic path length                                                      |

| Ν               | Number of coil turns                                                      |

| R               | Electrical resistance                                                     |

| $\Re$           | Total reluctance of magnetic circuit                                      |

| $\Re_c, \Re_g$  | Reluctance of core material and air gap respectively                      |

| Т               | Sampling period                                                           |

| tr              | Rise time                                                                 |

| t <sub>ui</sub> | Unit interval                                                             |

| υ               | Voltage across coil                                                       |

| $V_b$           | Rail supply                                                               |

| V(s)            | Load supply                                                               |

|                 |                                                                           |

| $Z_0$         | Characteristic impedance               |

|---------------|----------------------------------------|

| $\omega_s$    | Sampling frequency                     |

| $\omega_{wp}$ | Pole frequency for digital PID control |

| $\phi$        | Magnetic flux                          |

|               |                                        |

----

. .... . ...

### Chapter 1

# Introduction

Chapter 1 presents some background on active magnetic bearings (AMBs) and gives the problem statement for this thesis. An overview of the issues to be addressed and methodology is also presented, after which an overview of the document is given.

#### 1.1 Background

Active magnetic bearings (AMBs) comprise mechanical, electrical and electronic components that classify them as mechatronic products. This type of bearing is unique in the sense that there is no contact between rotor and actuator since the rotor is suspended using electromagnets.

Bearing stiffness, damping, rotor position and many other features can be actively controlled hence the name active magnetic bearings. These characteristics and a range of other advantages make AMBs attractive for application in turbomachinery, vacuum techniques, vibration isolation and application in space physics to name just a few [1].

#### 1.1.1 Basic active magnetic bearing operating principle

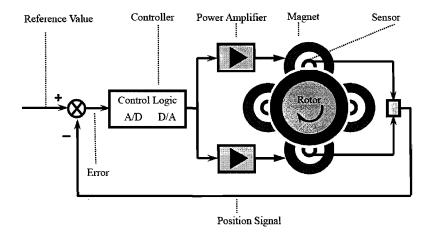

The active magnetic bearing constitutes three main parts: the actuators, position sensors and controller. The sensor measures deviation of the rotor from the reference position whilst the controller uses the sensor output to derive a control signal for the power amplifiers. The power amplifiers convert the control signal to a corresponding current. This current energises the electromagnets of the bearing to create an attractive force.

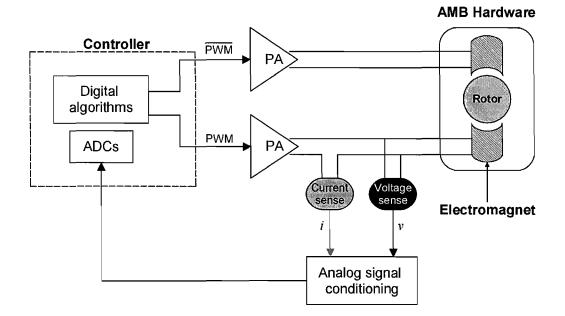

Figure 1.1 illustrates a simple representation of an AMB. In the figure an analogue to digital converter (ADC) and a digital to analogue converter are represented in the controller box. This

is consistent with the use of a digital controller. Digital controllers have a number of advantages over the use of an analogue controller.

Figure 1.1: Representation of AMB system [2]

#### 1.1.2 Digital Controller

Digital control is a preferred choice in today's digital society. Digital control presents advantages that renders it far more attractive than analogue control. Higher functionality can be achieved by using digital control rather than analogue control. The following are examples of functions that digital control can provide [1]:

- Procedures at start-up and shut down;

- Unbalanced treatment;

- Various filtering;

- Diagnosis;

- Monitoring.

Other advantages include [1]:

- More complex algorithms can be evaluated using digital control, which are impossible with analogue circuits;

- Digital control will reduce the susceptibility of noise on the system;

- Greater flexibility in the control algorithm implementation;

- Easier parameter adjustment;

- Real time monitoring and recording of operating conditions;

- Calibrating inputs are easier;

- Digital controllers reduce the amount of dedicated hardware, which make circuits more compact.

#### 1.1.3 System architecture

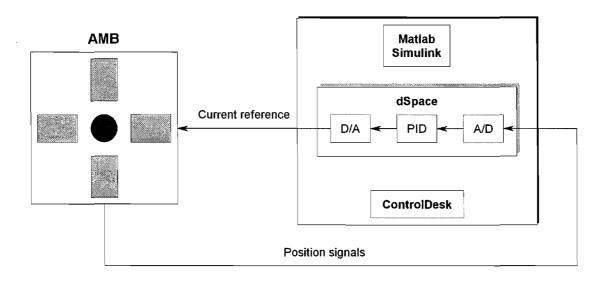

The McTronX research group possesses an AMB model that is controlled by a rapid prototyping control system called dSpace<sup>®</sup>. The dSpace<sup>®</sup> hardware consists of a controller card that slots into a PCI slot of the PC. The card has several digital and analogue inputs/ouputs (I/O) and has a microcontroller on-board. It has certain shortcomings such as it requires a PC and cannot function as a stand-alone system.

#### **Current system**

The dSpace card and software are specifically designed to enable real time control and monitoring of a system. The dSpace software is integrated with the MATLAB<sup>®</sup> and Simulink<sup>®</sup> environment, as illustrated in Figure 1.2. ControlDesk<sup>®</sup> is part of dSpace software which provides the functionality to control, monitor and automate experiments.

Figure 1.2: Current AMB control system configuration

#### **Proposed system**

Traditional AMB systems commonly use eddy current sensors for rotor position sensing. These sensors are expensive and contribute to a large portion of the total cost of an AMB system. Different techniques are being researched for determining the rotor position from the currents through the electromagnets of the AMB (see section 2.1). This is called self-sensing [3].

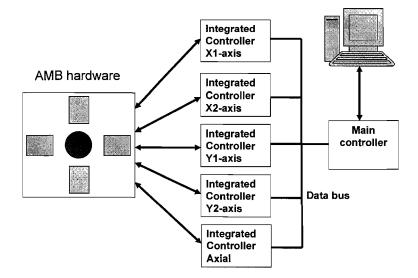

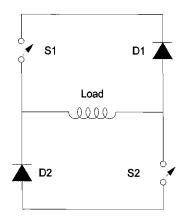

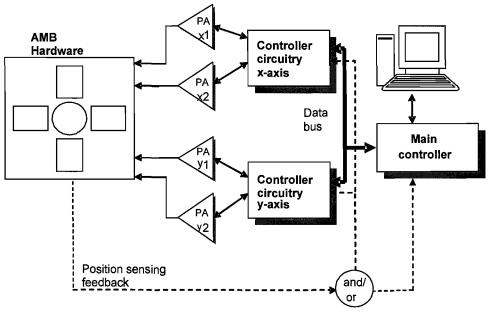

An integrated controller is to be developed that will be used to implement different self-sensing techniques, for differential drive mode. The model requires two power amplifiers for one degree of freedom. For example, vertical suspension requires a power amplifier for the top electromagnet and one power amplifier for the bottom electromagnet. Each integrated controller will have an embedded device for executing control algorithms and two power amplifiers.

Figure 1.3 illustrates a proposed configuration that utilizes integrated controllers. An integrated controller will be able to function as a stand-alone controller. By connecting multiple integrated controllers with each other, more complex control algorithms can be implemented and evaluated. This configuration will require a high speed communication bus between integrated controllers.

Figure 1.3: Proposed AMB control system configuration

#### **1.2** Problem statement

The purpose of this project is to develop an integrated controller for the purpose of providing an optimal platform for implementing and evaluating self-sensing techniques.

Each integrated controller shall be able to suspend the AMB in one degree of freedom and can be duplicated for the suspension of an AMB in multiple degrees of freedom.

The integrated controller will consist of analogue, digital and power electronics. A circuit board layout that incorporates analogue, digital and power components poses some unique design issues.

The embedded devices located on the integrated controllers must be able to execute algorithms including DSP functions such as filters and FFTs within specified time constraints.

#### 1.3 Issues to be addressed and methodology

The integrated controller is to be developed in collaboration with an industry partner. The decision to take this approach was based on the following:

- The McTronX group has a lack of experience in the development of digital hardware architectures. The industry partner on the other hand offers resources in terms of experienced designers as well as tested and verified functional designs.

- Detail design, and design verification were done by both the industry partner and McTronX. This ensured reliability and provided both the industry partner and MctronX insight into certain design issues.

- The MctronX group has the chance to gain valuable experience for future designs. Working with an external company requires detail project management for successful end-product development. McTronX research group will have knowledge on successful planning and management for collaborative projects.

- The collaboration between a well funded research group and a company adhering to very high development standards ensured a high quality end-product.

#### **1.3.1** Conceptual analysis

Certain aspects had to be considered in the conceptual analysis before the specification could drawn up. The following aspects will be briefly discussed: communication architectures, embedded devices, circuit design and printed circuit board (PCB) layout, firmware development.

#### **Communication architectures**

High speed communication has to be established between integrated controllers to relay data such as rotor position, reference current, status information etc.

Protocols and interface schemes will be considered and weighed against each other for robustness, speed, bus architecture capabilities etc. Common interfacing schemes typically used to connect controllers are: RS485, RS422, RS232 and CAN [4],[5],[6].

#### **Embedded devices**

The control scheme for the AMB determines the type of embedded device. The digital signal processor (DSP) and Field Programmable Gate Array (FPGA) each has their advantages, disadvantages and unique features that have to be considered in the design process.

Research data will be collected and tests conducted on available devices in order to evaluate embedded devices. Some considerations for the choice of the embedded device include: learning curve for using device, algorithms to be implemented on the device, device processing speed, device architecture etc [7].

#### Circuit design and printed circuit board (PCB) layout

The integration of an embedded device with the power amplifiers will require careful circuit design. Circuit design will involve digital, analogue and power circuits. Analogue circuits will include analogue to digital converters (ADCs), filters and power supply circuits. The digital circuits will incorporate external RAM, the embedded device itself, communication line drivers and other peripheral circuits. The power circuit will incorporate switching devices in two- and three-phase bridge topologies.

Once a circuit layout has been designed, the circuit need to be etched on a PCB. A PCB layout design for such a complex system demands time and experience. Issues to be considered in PCB layout include, proper grounding, filtering, shielding and cabling to name just a few[8].

The circuit design and PCB layout in the development of the integrated controller has been identified as high risk factors. In order to reduce the risk the design of the digital circuitry, PCB layout and integration will be sub contracted to the industry partner.

#### Firmware development

In combination with the development of the hardware for the integrated controller, firmware has to be designed and implemented on the embedded devices.

The firmware for the embedded device will then be coded in an appropriate language and compiler. If a Texas Instruments (TI) DSP device is used, Code Composer Studio (CCS) will be utilized for firmware development. For Xilinx FPGAs, Xilinx's ISE will be used for firmware development in VHDL.

For development and testing purposes it is useful to know what is happening in the embedded code of the embedded device in real time. Emulation devices are available that enable the real time monitoring and controlling of firmware.

#### 1.3.2 System specification

A system specification will be compiled. The specification will include technical guidelines for the development of the integrated controller. The compiled specification will be distributed to a sub-contractor to provide guidelines for the hardware development.

The project will thus be managed by performing system engineering functions which will constitute part of the study.

#### **1.3.3** Sub-system procurement

Four sub systems have been identified: the power amplifiers, the digital electronics, analogue electronics and firmware. Each of these sub systems need to be developed and integrated.

#### **1.3.4** System integration

Each sub-system, power amplifiers, digital electronics, analogue electronics and firmware has to be integrated to constitute the complete system of the integrated controller.

The system specification will ensure that all sub-components can be properly integrated by specifying the interfaces and their technical requirements. The integration of the sub-systems will also constitute part of this study.

#### **1.3.5** System evaluation

The integrated control system for the AMB has to be evaluated and tested. Predicted results will be evaluated with the use of measurements and inspection. The system can then be characterized and verified using the tests results obtained. Recommendations and conclusions will be derived.

#### **1.4 Document overview**

A brief overview of this thesis will now be given:

#### 1.4.1 Chapter 2: Literature study

Chapter 2 will present detail on literature knowledge obtained through the course of this thesis. Aspects such as self-sensing, embedded devices, communication interfaces and systems engineering will be addressed.

#### **1.4.2** Chapter 3: System specification

A detail specification was drawn up for the development of the integrated controller. The specification is a combination of a type A and B specification. In Chapter 3 an adapted version of the specification is presented to help guide the reader's understanding of the integrated controller's structure and functions.

#### **1.4.3** Chapter 4: Sub-system design and evaluation

In the specification certain choices were made regarding functional architecture units. Chapter 4 strives to motivate these choices, specifically the choice of embedded devices and the communication interface. An experimental laboratory configuration evaluates RS485 communication. Theoretical predictions are made in the amount of processing power that will be required for the implementation of certain algorithms that the integrated controller will be designed to execute.

#### 1.4.4 Chapter 5: Integrated controller hardware and evaluation

Chapter 5 presents the integrated controller hardware. Key components of the hardware are marked and referenced back to the specification to show traceability from specification to actual product. The integrated controller is then evaluated. First the sub-components are evaluated and then the complete system is integrated and evaluated.

#### **1.4.5** Chapter 6: Conclusions and recommendations

Chapter 6 concludes that the integrated controller's evaluation reveals compliance to the specification. Recommendations for future work is also discussed.

## **Chapter 2**

# Literature study

Chapter 2 provides details on aspects that played a key role in the development of an active magnetic bearing. Because self-sensing research is the main driving force behind the development of the integrated controller, some aspects of self-sensing will be discussed. Furthermore processors, communication interfaces and systems engineering will enjoy attention. Systems engineering will be applied since the integrated controller is developed in collaboration with an industry partner.

#### 2.1 Self-sensing

In a traditional AMB system the rotor position is determined with the use conventional sensors. Expensive eddy current sensors are commonly used in AMB applications. Self-sensing strives to eliminate these sensors and extract the position information using alternative techniques. Self-sensing provides some advantages. To name a few [3]:

- Fewer components in the system implies fewer components that can malfunction.

- In smaller systems the cost is reduced significantly by eliminating dedicated position sensors

- Self-sensing could be used as a backup measure when sensor failure occurs (redundancy).

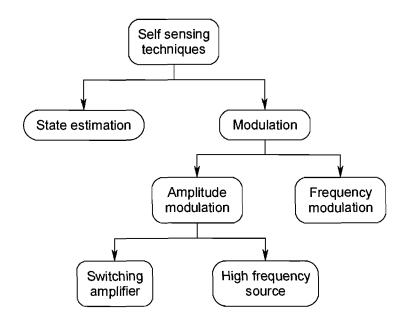

There are basically two main types of self-sensing techniques as illustrated in Figure 2.1, state estimation and modulation. This thesis concentrates on developing hardware suitable for implementing modulation based self-sensing.

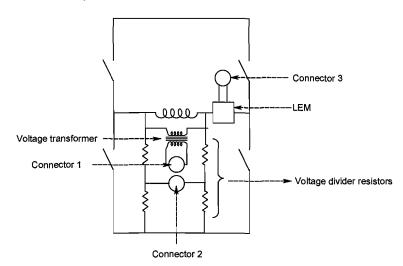

The modulation based self-sensing technique is based on extracting the position information from the currents and voltages in the electromagnetic coils. Figure 2.2 shows a block diagram representation of a modulation self-sensing setup for one degree of freedom on the AMB.

Figure 2.1: Types of self sensing [3]

Figure 2.2: AMB self-sensing setup

#### 2.1.1 Basic magnetic bearing model

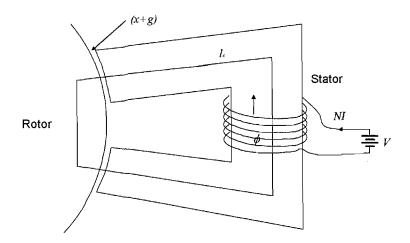

To motivate the study into the self-sensing technique further, a simple model for a magnetic bearing will now be derived. The model is adapted from the work of Schammass [3]. This will illustrate the relationship between the changing current in the electromagnetic coil and the position of the rotor. The magnetic circuit in Figure 2.3 is considered.

Figure 2.3: Magnetic circuit

Applying Faraday's law of inductance to the circuit, (2.1) can be formulated

$$v = N \frac{d\phi}{dt} + iR \tag{2.1}$$

with:

- v : voltage across the coil;

- *N*: number of turns;

- *R* : coil resistance;

$\phi$  : flux;

*i* : current in coil.

The equation for flux is given as

$$\phi = \frac{Ni}{\Re} \tag{2.2}$$

where  $\Re$  is the reluctance of the magnetic circuit.

For this circuit the reluctance is divided into two parts; the reluctance of the air gap and the reluctance of the magnetic material. By summing the two reluctances (2.3) is obtained.

$$\Re = \frac{2(g \pm x) + {}^{l_c}\!/{\mu_r}}{\mu_0}$$

(2.3)

With:

- g : nominal air gap;

- x : change in the air gap;

- A: cross sectional area of stator;

- $l_c$  : magnetic path length;

- $\mu_r$ : relative permeability of material.

The inductance of the coil is calculated as follows:

$$L = N \frac{\partial \phi}{\partial i} = \frac{\mu_0 N^2 A}{2(g \pm x) + \frac{l_c}{\mu_r}}$$

(2.4)

It can thus be seen that the inductance of the actuator is inversely proportional to rotor position. Substituting (2.4) into (2.1) provides the coil current equation.

$$\frac{di}{dt} = \frac{2(g \pm x) + \frac{l_c}{\mu_r}}{\mu_0 N^2 A} (v - iR)$$

(2.5)

From (2.5) it can be seen that variation of the current in the coil is proportional to the movement of the rotor.

#### 2.1.2 Amplitude modulation approach

Amplitude modulation is a technique used to obtain the position information from the switching power amplifier outputs. The current signal contains the position information and the voltage signal contains the duty cycle variations of the power amplifier.

Signal processing in the digital domain provide a number of advantages that will be discussed further in Section 2.2.1. Because of these advantages, self-sensing techniques can be implemented both in the analogue and digital domain, or can be implemented exclusively in the digital domain.

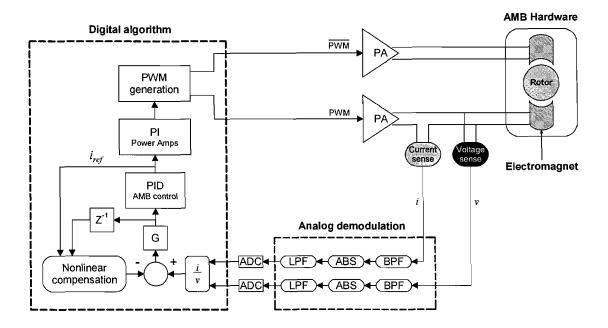

Figure 2.4 illustrates the amplitude modulation based on the work of Schammass [3] for one degree of freedom on the AMB. To explain the self-sensing technique further, a few waveforms will be shown at various stages of the demodulation process.

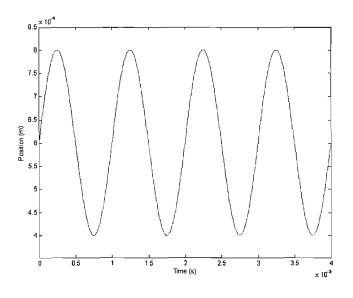

Figure 2.5 shows the position of the AMB's rotor with a sinusoidal disturbance. It should be noted that this signal is not the actual measurement of an AMB's rotor position but only a generated signal for illustration purposes.

A modulated current through a coil of the AMB, under ideal circumstances, is shown in Figure 2.6. The carrier frequency is the switching frequency of the power amplifier, and the modulation component is the changing inductance due to the change in rotor position.

Figure 2.4: Amplitude modulation self sensing

Figure 2.5: Actual position of rotor

In the system the modulated current will be sensed by a current sensor and passed through a band pass filter (BPF). The BPF produces the fundamental components of the current and voltage signals. Illustrated in Figure 2.7 is the band pass filtered current signal.

The absolute (ABS) value of the signal is obtained and low pass filtered (LPF) to produce the envelope of the signal. The envelope of the current signal can be seen in Figure 2.8. Only low sampling ADCs is necessary for digitizing the envelope components because they will be no higher than 500 Hz, which is the bandwidth of the AMB.

------

Figure 2.6: Modulated current

Figure 2.7: Current after band pass filter

In the digital domain the demodulated current is divided by the demodulated voltage to compensate for duty cycle changes. The output of the division is already an estimation of the rotor position but is unscaled and contains no compensation for non-linear effects. The non-linear effects are caused by, for instance, the B-H curve of the magnetic material used in the electromagnets. The self-sensing algorithm needs to compensate for nonlinear material effects. This is done by using one delayed position estimation and the reference current. Further details on this compensation algorithm is beyond the scope of this thesis.

Other strategies may be implemented for demodulating the current and voltage signals. For

Figure 2.8: Current after low passed filter

instance, directly after analogue band pass filtering, the high frequency signal can be sampled by a high sampling ADC, typically in the range of 1 Msps. This high sampling rate will ensure proper representation of the 20 kHz signal in the digital domain. Sampling a 20 kHz signal at 1Msps will result in having 50 data points for every 50 µs time period.

After sampling a processor can perform a fast fourier transform (FFT) on the signal and obtain the peak amplitude value of the FFT. The peak value is used for estimating the rotor position. This technique is illustrated in Figure 2.9 which shows only the current demodulation. Voltage demodulation is performed in exactly the same manner.

Figure 2.9: Demodulation using an FFT

Another possible technique is illustrated in Figure 2.10. For this technique the ADC needs to sample exactly on the peaks of the fundamental frequency voltage and current signals. The peak values can again be used for a rotor position estimation.

Figure 2.10: Demodulation using synchronous sampling

Some of the techniques requires less digital processing than others. The FFT technique will for instance require a lot more processing resources than the simple analogue modulation technique. All of the techniques can also be fully implemented in the digital domain. In order to adequately investigate different self-sensing techniques a powerful processor is required that offers flexibility and performance.

## 2.2 Processors

Digital signal processing (DSP) has become a indispensable part of industrial applications such as telecommunications, digital television, digital audio, instrumentation and cellular phones to name just a few. DSP architectures are becoming cheaper and more commonly available, and thus poses more attractive design solutions for signal conditioning applications [9].

The designer of a system is often faced with a choice between analogue signal conditioning and DSP. Because of the many advantages of DSP, as will be discussed in section 2.2.1, it might be more appealing to perform signal conditioning in the digital domain. A variety of architectures are available to the designer for implementing DSP. In the following sections (2.2.1 and 2.2.2) two possible architectural choices will be discussed: Digital Signal Processors (DSPs) and Field Programmable Gate Arrays (FPGAs).

## 2.2.1 Digital signal processors (DSP)

Digital signal processors (DSPs) contain specialized architecture that enables it to be much more efficient at digital signal processing than general purpose processors (GPP) [10].

**Advantages** - DSP offers some significant advantages over analogue signal conditioning. Some of these advantages include [9],[10]:

- Digital signals can be sent over large distances without losing data;

- Using analogue components to filter signals is expensive and requires fixed detailed design of components. Digital filtering is flexible in the sense that the programmed code can be reconfigured;

- Perfect copies can be made of digital signals where copied analogue signals decay with each copy;

- Performance of the digital processor doesn't change with temperature or age;

- DSPs can be used to perform functions not possible with analogue signal processing.

**Disadvantages** - As with any engineering application, DSP has some drawbacks that needs to be weighed against the advantages [9]:

- Speed and cost: DSPs can be expensive, especially when large bandwidth is a requirement. Analogue to digital converters (ADCs) and Digital to Analogue Converters (DACs) are either too expensive or cannot provide enough resolution for high bandwidth DSP. DSPs are only fast enough to process signal with a moderate bandwidth. Analogue processing is still used for signals in the 100 MHz range.

- Design time: Without the necessary resources and sufficient knowledge in DSP techniques, DSP design can be very difficult and time consuming.

- Finite word length: The amount of bits used to represent data should be carefully chosen as not to degrade system performance.

## **Design considerations**

Before any design can be initiated the requirements of the user need to be determined and a list of design constraints should to be drawn up. Some important characteristics to consider when choosing a digital signal processor are the following [9],[10]:

- **Programmability** The end product may either be application specific or general purpose (programmable). Programmable devices are more flexible and the developers can then easily change functionality for specific needs.

- **Throughput** Some applications need data to be processed and outputted faster than in other applications. For example high definition TV (HDTV) needs decoding in the Mega bits per second range (Mbps) where motor control only need a bit rate in the thousands of bits per second (kbps) range.

- **On-chip memory -** The amount of on-chip memory significantly influences the physical silicon size of a chip, and thus also the price. The advantages of on-chip memory are also worth mentioning though:

- Eliminates need for external memory and reduces board space;

- Access performance is increased and thus also overall throughput performance;

- Lower power consumption.

- Integration Processors may have a variety of on-chip peripherals, reducing the need for external devices. A variety of options are available and should be considered by the designer.

- **Power** Power dissipation will be more crucial in handheld devices than devices that plug into a power outlet such as a wall socket. Chips that consume less power are more expensive but might be worth considering in certain applications.

- **Real-time responsiveness -** "Real-time" refers to the ability to perform a task within a limited time frame. Different processors operate at different speeds and it is up to the designer to decide if the processor will meet the real-time constraints. The speed of a processor is typically measured in Million Instructions Per Second (MIPS).

- **Type of arithmetic -** Floating point and fixed point arithmetic are typically used in DSPs. Floating point arithmetic represents numbers in the form of a mantissa and an exponent value, and is used in applications with a wide dynamic range. The dynamic ranges of signals differ in each application. Dynamic range can be considered as the difference in the largest and smallest value of a signal to be represented. Fixed point arithmetic represents only integer values, and is used in cheaper, high volume applications.

- **Word length** The higher the word length the more accurately signals can be represented in the digital domain. Simplistically one may conclude that higher word lengths will result in for example better audio quality, but will require more resources (memory, MIPS) from the DSP.

- **Standards -** Standards often specify certain performance requirements that must be taken into account when designing a system.

**High availability -** In some applications availability is crucial. For example if a telephony system crashes, replacement parts need to be available.

### DSP on-chip technology

As mentioned in the first paragraph of Section 2.2.1 a DSP has a specific architecture that increases its performance when executing DSP functions. Some built in technologies that make this possible include the following [9],[10]:

**Multiply and accumulate unit (MAC) -** Signal processing involves a great deal of multiplication, when considering for instance (2.6).

$$result = x_1 * c_1 + x_2 * c_2 + x_3 * c_3 + \dots x_n * c_n$$

(2.6)

A DSP has built in architecture that can perform the multiplication of two numbers and the adding of the result to all previous multiplications, in one clock cycle.

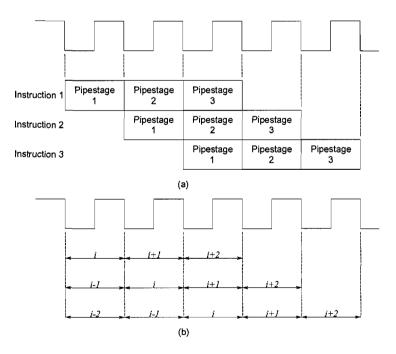

**Pipelining -** An instruction can be broken down into three steps, that is instruction fetch, decode and execute.

Figure 2.11(a) illustrates that with overlapping a new instruction can be started every clock cycle.

Figure 2.11: Illustration of pipelining [9]

In Figure 2.11(b) one can see that three operations can be executed simultaneously:

- the *i*<sup>th</sup> instruction is fetched;

- (*i*-1) <sup>th</sup> instruction is decoded;

- (*i*-2) <sup>th</sup> instruction is executed.

- **Code density with very long instruction words (VLIW) -** VLIW is an instruction that represents several operations executed at the same time by the DSP.

- **Harvard architecture -** The Harvard architecture specifies memory where data and code lie in separate spaces. This enables the DSP to simultaneously fetch the next instruction and execute the current instruction.

- **Zero overhead looping -** Typical DSP algorithms have what is known as a critical loop. An algorithm, for example voice decoding, is executed many times within a loop. Loop management in GPPs requires many clock cycles. In DSPs a special architecture manages the loop. The result is that the management of the critical loop requires zero clock cycles.

- **Circular buffers -** In functions such as Finite Impulse Response (FIR) filters, memory of previous values are required. Developers use a circular buffer to implement the delay line (list of previous values) efficiently. This involves re-using a small block of memory and wrapping back to the top if the bottom is reached. In DSPs built-in architecture can manage circular buffers and eliminate extra overhead processing.

DSP technology, if correctly implemented, may greatly improve the efficiency of processing digital signals. Although DSP offers some degree of simultaneous processing with pipelining technology, it still lacks true parallelism. Field programmable gate arrays (FPGAs) can perform a large number of instructions every clock cycle.

## 2.2.2 Field programmable gate array (FPGA)

A microprocessor has a fixed hardware architecture and runs a program. In the case of an FPGA, the programmability is intended at the hardware level. The code implemented on an FPGA is thus used to reconfigure the hardware setup of an FPGA [11].

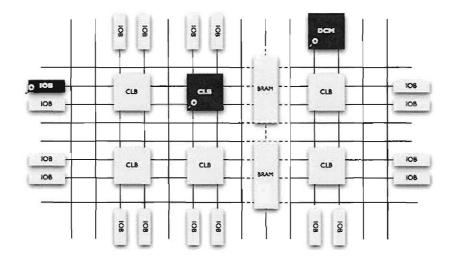

The basic architecture of an FPGA is based on configurable logic blocks (CLBs) with programmable interconnects or switch matrices. Figure 2.12 illustrates a block architecture of a FPGA with the following basic components[11],[12]:

**Configurable logic block (CLB)** - The CLB is the basic logic unit of an FPGA that constitutes a reconfigurable switch matrix with 4 or 6 inputs, selection circuitry (Multiplexer, etc) and flip-flops. The switch matrix can be configured to manage RAM, combinational logic or shift registers.

- Interconnect Flexible interconnections provide routing of signals between CLBs, and also routes signals to/from the Inputs/Outputs (I/Os).

- SelectI/O Modern FPGAs provide a wide variety of I/O standards allowing the designer to select the ideal system interface. I/Os are arranged in banks, each bank providing different I/O standards for interfacing.

- Memory Embedded block memory enables the designer to include on-chip memory in designs.

- **Complete clock management -** Xilinx FPGAs have build in digital clock managers that reduce jitter and phase-locked loops for clock synthesis.

Figure 2.12: FPGA structure [12]

## VHDL

The acronym VHDL stands for VHSIC Hardware Descriptive Language, where VHSIC is the abbreviation for Very High Speed Integrated Circuits. The application of VHDL includes the programming of FPGAs, Configurable Logic Devices (CPLDs) and Application Specific Integrated Circuits (ASICs) [11].

The execution of VHDL statements are inherently parallel. For this reason VHDL is referred to as code rather than a program. Statements can be placed inside certain keyword program blocks such as PROCESS, FUNCTION or PROCEDURE that will force the code to be executed sequentially [11].

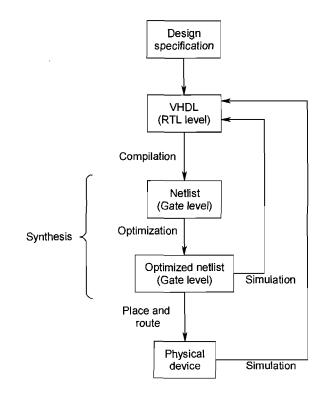

Figure 2.13 illustrates a simplified design flow of VHDL code. A design specification is drawn up that specifies how the final design is required to behave.

Figure 2.13: VHDL design flow summery [11][13]

A register transfer level (RTL) description is created which is basically the VHDL code. An editor is used for creating the VHDL code and saved with the extension .vhd. The code is synthesized into a netlist which is descriptive of the RTL at gate level and can be optimized for either speed or area [11],[13].

Simulations are run next which is an important part of the design process. The designer uses the simulations to verify the design. If simulation results are unsatisfactory, the VHDL needs to be edited and re-synthesized [11],[13].

Place and route software is used to generate the physical layout on a target device such as an FPGA. Place and route does the following [13]:

- The netlist's basic functions (primitives) are placed into an appropriate location on the target device.

- Signals are routed between the primitives according to the netlist design.

Post route simulation is the final verification process before the device is programmed. Post route simulation checks whether the place and route process was successful by verifying that the design will meet the specified constraints (for example timing constraints). The post route simulation is run after the place and route process has been executed [13].

## Summary

Digital Signal Processors might have architectures specifically designed for DSP based operations, but might still suffer to meet demanding real time constraints. The FPGA offers high speed processing of algorithms that would benefit from parallelism, such as FFTs and FIR filters. Implementing the FPGA as a co-processor to the DSP will greatly increase performance and yield a very powerful hardware system capable of processing complex algorithms in real time [14],[15].

## 2.2.3 Co-processing

In many applications only 20 % of the code on a DSP will use up 80 % of its processing power (MIPS). This 20 % represents the core algorithms in the application. The other 80 % of the code is responsible for execution control and initialization. The designer is faced with reducing the processing load of the 20 % along with trying to limit the complexity of the remaining 80 % [15].

A co-processor is ideal in this situation for offloading some of the load caused by the power hungry 20 % code. The designer must now determine exactly what is to be offloaded to the co-processor [15].

For this the designer can use the development tools of the DSP. Texas Instruments' Code Composer Studio (CCS) provide profiling functions that can be used to indicate the amount of resources a particular function is consuming. Some criteria by which to consider the algorithms to be offloaded are [15]:

- The algorithms should at least be responsible for half of the processor load;

- Clustered algorithms, that are only dependent on onr another's outputs, will limit the co-processors dependency on the DSP. The DSP only has to send data for the co-processor and receive the result without having to interfere with the co-processor's operations.

- Implementing the algorithms should be easily implementable on the hardware and have a repetitive structure.

The interface between the DSP and co-processor is dependent on the peripheral hardware on the DSP. For Texas Instrament's DSPs, possible options include 16/32/64-bit Extended Memory Interface (EMIF) and Multichannel Buffered Serial Ports (McBSP) [15].

## 2.3 Communication

Consider an AMB controller system such as the one depicted in Figure 1.3. The system constitutes a main controller and several slave controllers. Some form of data transfer link is required between the main and slave controllers. Data transfer is also necessary for data logging and analysis. This might imply a convenient interface link to a PC such as a USB or RS232 connection. The next three sections discuss three industry standard interface protocols that are frequently used in a wide variety of applications. They are: Controller Area Network (CAN), RS232 and RS485.

## 2.3.1 CAN bus

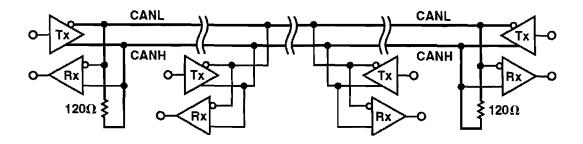

The Controller Area Network (CAN) bus architecture was originally developed for use in cars to replace complex wiring systems. It is a robust protocol that has the ability to self diagnose and repair data errors. The protocol specifies a 2-wire differential signal on the physical level and thus gives the CAN-bus excellent noise immunity. Figure 2.14 displays a typical CAN bus. The CAN bus can support up to 30 nodes on the bus [5],[16].

Figure 2.14: CAN bus [5]

The CAN bus driver produces a differential signal that constitutes high and low voltage, that is placed on the CANH and the CANL signal wires respectively. Together the high and low voltages form the dominant signal on the bus that represents a logic low. When no node/transmitter is transmitting, pull up resistors drive the bus to Vcc/2, where Vcc is the supplied voltage to the transmitter. This is the recessive signal level and represents a logic high. Figure 2.15 illustrates these levels. In the dominant state, CANH is typically (Vcc-0.9 V) and CANL is 1.5 V [5],[16].

Table 2.1 summarises the CAN bus specifications.

Figure 2.15: CAN bus signals [5]

| Max Speed | Max Distance | Transmission | Signal       | Multipoint | Robustness |

|-----------|--------------|--------------|--------------|------------|------------|

| 1 Mbps    | 40 m         | Asynchronous | Differential | Yes        | High       |

## 2.3.2 RS232

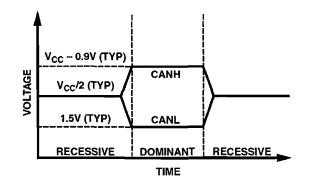

RS232 is not a very fast or reliable communication protocol but is easy to design and implement. The RS232 driver produces a large drive voltage of  $\pm$ (5 to 15 V). The receiver is triggered by signals above 3 V or below -3 V and are unbalanced. This implies that the signal levels are referred to ground. A logic 0 will be detected if the signal is above 3 V relative to ground and a logic 1 will be detected when the signal is below -3 V relative to ground [16],[4]. A RS232 bus and its signal levels are illustrated in Figure 2.16.

The RS232 protocol specifies some control signals in addition to the data signals. These control signal may or may not be used in the communication setup. They are the following:

- DCD Data carrier detect

- DSR Data set ready

- RTS Request to send

- CTS Clear to send

- DTR Data terminal ready

- RI Ring indicator

Summarised in table 2.2 is the RS232 specifications.

Figure 2.16: RS232 bus [4]

| Table 2.2: | RS232 | specifications |

|------------|-------|----------------|

|------------|-------|----------------|

| Max Speed | Max Distance | Transmission | Signal     | Multipoint | Robustness |

|-----------|--------------|--------------|------------|------------|------------|

| 1 Mbps    | 20 m         | Asynchronous | Unbalanced | No         | Low        |

## 2.3.3 RS485

RS485 supports multipoint architecture, which implies that there can be multiple drivers interfaced with multiple receivers. These interfaces specify balanced data transmission schemes. This makes the interface robust and capable of operating in noisy environments [17].

The voltages used for logic levels appear across a pair of signal lines that transmit only one signal. The terminals of the receiver and its connector does have a ground connection but the logic level is not referred to this ground [4].

The logic states are defined as follows [4]:

- When the voltage on terminal A of Figure 2.17 is negative with respect to the voltage on terminal B, a logic 1 will appear on the output of the receiver.

- When terminal A is positive with respect to terminal B, the line is a logic 0.

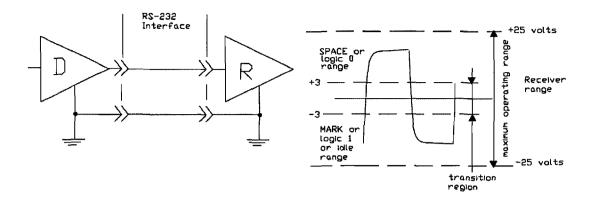

### **Differential receiver**

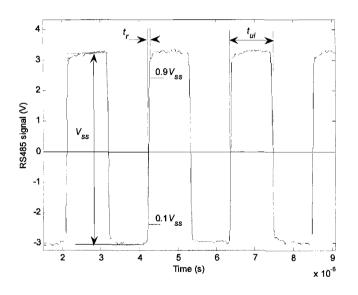

The RS485 receiver can tolerate a maximum common mode voltage (Vcm) of -7 V/+12 V. The common mode voltage is defined as the mean voltage of terminals A and B with respect to signal ground. If the differential input voltage (V) is greater than 200 mV, a logic state will appear on the output of the receiver. When the differential voltage is less than -200mV, the inverse logic state will appear on the output of the receiver [4][17].

-----

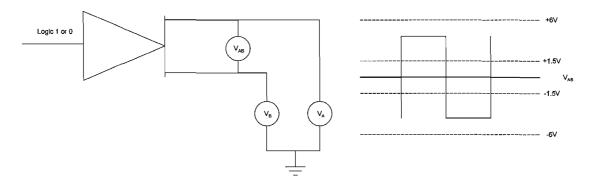

Figure 2.17: RS485 receiver and signal levels

### **Differential transmitter**

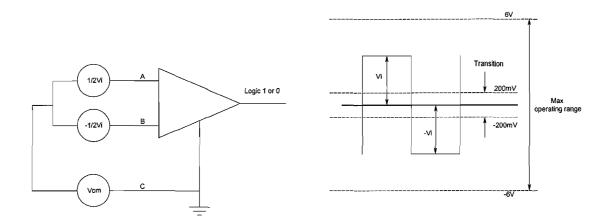

The differential voltage  $V_{AB}$  generated will stay inside hte ranges 1.5 V to 6 V and -6 V to -1.5 V as illustrated in Figure 2.18.

Figure 2.18: RS485 transmitter and signal levels

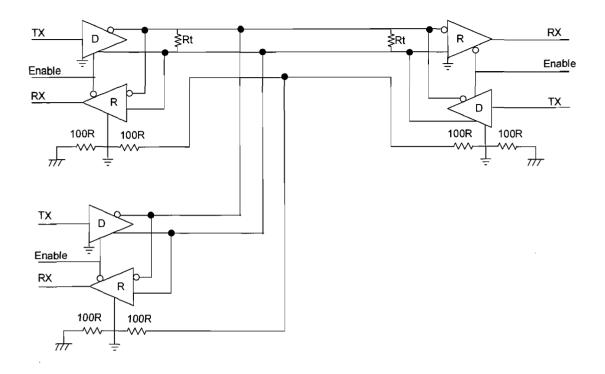

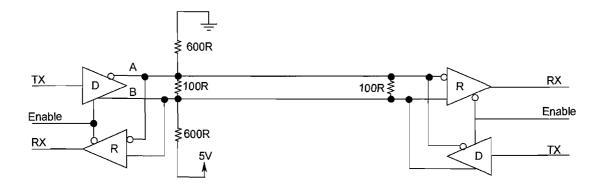

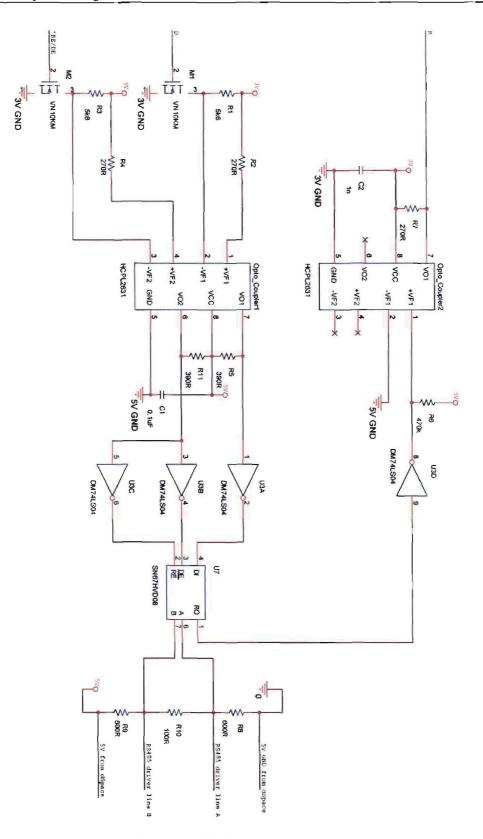

Figure 2.19 shows a typical multidrop RS485 network. The enable line is used to enable or disable the driver. A logic 1 enables the driver and a 0 disables the driver. When the driver is disabled, it is put into the tristate condition. This effectively disconnects the driver from the line and is necessary to permit other drivers to send data over the same transmission line. If two drivers try to transmit data at the same time, erroneous data might occur. This is called line contention.

RS485 specifications can be summarised in table 2.3.

Figure 2.19: RS485 bus

| Table 2.3: | RS485 | specifications |

|------------|-------|----------------|

|------------|-------|----------------|

| Max Speed | Max Distance | Transmission | Signal       | Multipoint | Robustness |  |  |

|-----------|--------------|--------------|--------------|------------|------------|--|--|

| 20 Mbps   | 1.2 km       | Asynchronous | Differential | Yes        | High       |  |  |

## 2.4 Systems Engineering

Because systems engineering is such a loose term it is appropriate to start off with a description of a few concepts. The general definition for a system as adapted from [18] is:

An assemblage or combination of things or parts forming a complex or unitary whole: a mountain system or a railroad system; any assemblage or set of correlated members: a system of currency; an ordered and comprehensive assemblage of facts, principles, doctrines, or the like in a particular field of knowledge or thought: a system of philosophy; a coordinated body of methods or a scheme or plan of procedure: a system of government; any formulated, regular, or special method or plan of procedure: a system of marking, numbering, or measuring; the world or universe.

For the purpose of this section it is necessary to narrow the definition of a system down to an engineered system. Some recognizable traits of an engineered system can be summed up as follows [19]:

- "Engineered systems have a *functional purpose* in response to an identified need and have the ability to achieve some stated *operational objective*.

- Engineered systems are *brought into being* and *operate* over a life cycle, beginning with a need and ending with a phase out and disposal.

- Engineered systems comprise a *combination of resources*, such as humans, information, software, materials, equipment, facilities, and money.

- Engineered systems comprise of *subsystems* and related *components* that *interact* with one another to produce the systems response or behaviour.

- Engineered systems are part of a *hierarchy* and are influenced by external factors from larger systems of which they are a part.

- Engineered systems are *embedded* into the natural world and *interact* with it in desirable as well as undesirable ways."

The product might be considered only a part of a complete system, for instance the engine of an automobile. A product might also be the system itself, for example an air traffic control system that converts air traffic mayhem into an organized flow. Consumable products include bread, lubricants, batteries, solder paste, anything that cannot be repaired. Repairable products, e.g. forklift, guidance system or machine tools are often called *prime equipment* when it serves a larger system purpose.

Classical engineering is more concerned with the final product's performance than with the process of developing the product. It tries to find the most economical way, with the least resources, to develop a product that will improve the lives of people [19].

No product can come into existence without a development and construction process, and cannot keep functioning without maintenance and support. Systems engineering may be considered as the management of all aspects in the life cycle of a system. No one formal definition exists for systems engineering, and is more dependent on an individual's experience or the organization wherein it is used. The following are two published definitions [19]:

"An interdisciplinary approach encompassing the entire technical effort to evolve into and verify an integrated and life-cycle balanced set of system people, product, and process solutions that satisfy customer needs. Systems engineering encompasses (a) the technical efforts related to the development, manufacturing, verification, deployment, operations, support, disposal of, and user training for, system products and processes; (b) the definition and management of the system; (c) the translation of the system definition into work breakdown structures; and (d) development of information for management decision making." [20]

"An interdisciplinary collaborative approach to derive, evolve, and verify a life cycle balanced system solution which satisfies customer expectations and meets public acceptability." [21]

The following sections discuss some system engineering concepts that is adapted from [19].

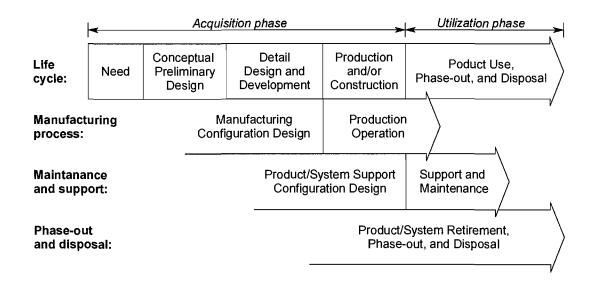

## 2.4.1 System life-cycle

It is important to understand the life cycle of a system in order to apply system engineering concepts. The product life cycle, as illustrated in Figure 2.20, starts at a need, followed by a conceptual design, detail design, production and finally product use and disposal.

Figure 2.20: Product and system life cycles [19]

Some of the system's life cycles that are often neglected, but equally important, are the manufacturing, maintenance and support, and product retirement. These life cycles should run in parallel with the product life cycle. The design of the system should not just focus on the product itself but should also consider operational outcomes that include producibility, reliability, maintainability, usability, supportability, serviceability and disposability.

## 2.4.2 System specification

In the conceptional design phase of a system life cycle, it is necessary to specify an overall guideline for system design. This top level *system specification*, also referred to as a Type A specification, will provide a baseline for development of lower level specifications: *development* (Type B), *product* (Type C), *process* (Type D) and *material* specifications (Type E).

A Type A specification includes the resulting specifications obtained from activities such as a *system feasibility analysis, system operational requirements, maintenance and support concept, technical performance measures* and *functional analysis and allocation*.

## System feasibility analysis

After having identified a need for a system, it is necessary to explore various design approaches. The approaches should be evaluated and the most feasible one identified in terms of performance, effectiveness, difficulty of design and production, maintainability, cost and other resources that will be required.

### System operational requirements

The next step after having decided on the design approach, operational scenarios need to be identified. Questions to ask are: "What are the anticipated type and quantities of equipment, software, personnel, facilities, etc., required, and where are they to be located? How is the system to be utilized, and for how long? What is the anticipated environment at each operational site? How is the system to be supported and for how long?" [19] By answering these questions the operational requirements for the system can be set up.

#### Maintenance and support concept

The maintenance part of the system is often neglected in the design phases as a result of the focus only being on the performance of the system. The system and its elements should be designed in such manner that they can be effectively maintained throughout their life cycle. Maintenance can be preventative and/or corrective.

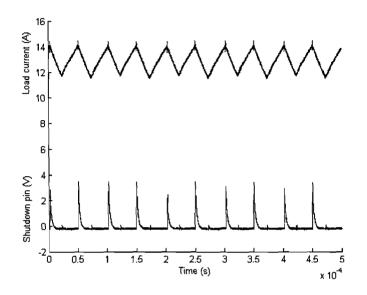

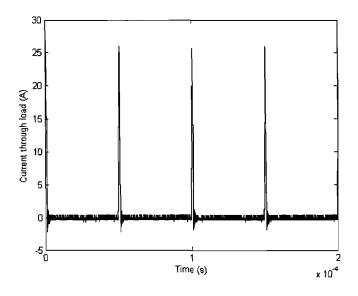

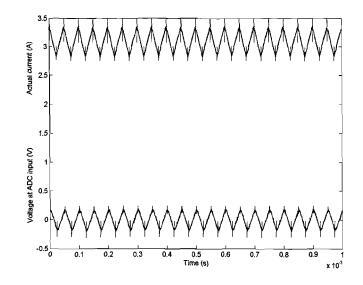

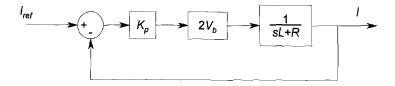

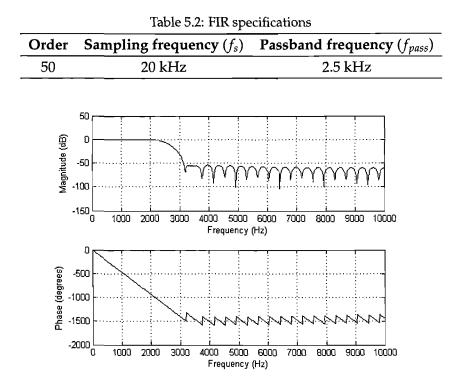

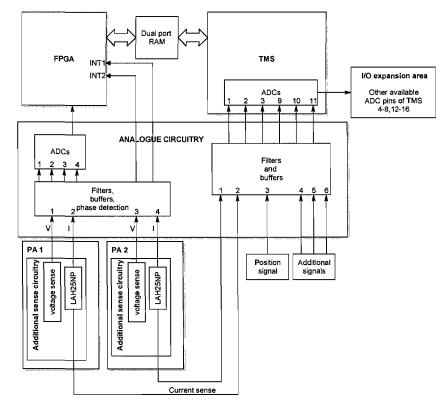

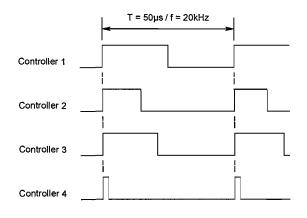

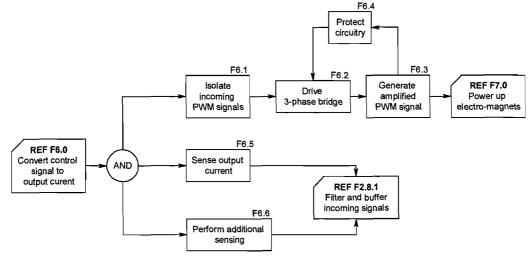

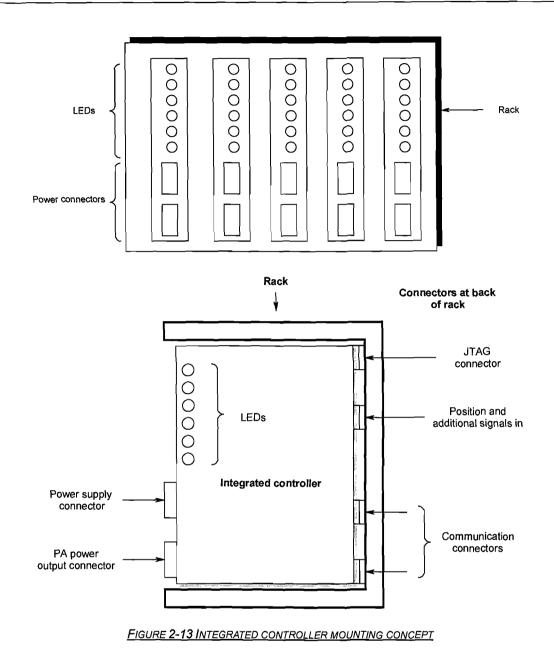

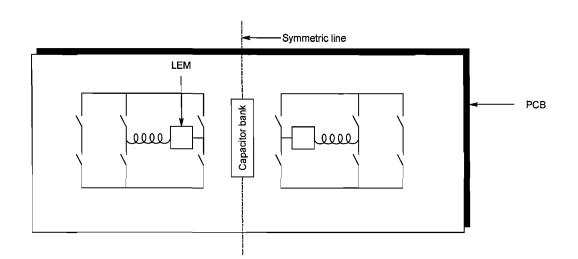

#### **Technical performance measures**